# Sun<sup>™</sup> Ultra<sup>™</sup> 60 Service Manual

Sun Microsystems, Inc. 901 San Antonio Road Palo Alto, CA 94303-4900 U.S.A. 650-960-1300

Part No. 805-1709-12 Revision A, August 2001

Send comments about this document to: docfeedback@sun.com

Copyright 2001 Sun Microsystems, Inc., 901 San Antonio Road, Palo Alto, CA 94303-4900 U.S.A. All rights reserved.

This product or document is distributed under licenses restricting its use, copying, distribution, and decompilation. No part of this product or document may be reproduced in any form by any means without prior written authorization of Sun and its licensors, if any. Third-party software, including font technology, is copyrighted and licensed from Sun suppliers.

Parts of the product may be derived from Berkeley BSD systems, licensed from the University of California. UNIX is a registered trademark in the U.S. and other countries, exclusively licensed through X/Open Company, Ltd.

Sun, Sun Microsystems, the Sun logo, AnswerBook2, docs.sun.com, and Solaris are trademarks, registered trademarks, or service marks of Sun Microsystems, Inc. in the U.S. and other countries. All SPARC trademarks are used under license and are trademarks or registered trademarks of SPARC International, Inc. in the U.S. and other countries. Products bearing SPARC trademarks are based upon an architecture developed by Sun Microsystems, Inc. The Energy Star logo is a registered trademark of EPA.

The OPEN LOOK and Sun<sup>™</sup> Graphical User Interface was developed by Sun Microsystems, Inc. for its users and licensees. Sun acknowledges the pioneering efforts of Xerox in researching and developing the concept of visual or graphical user interfaces for the computer industry. Sun holds a non-exclusive license from Xerox to the Xerox Graphical User Interface, which license also covers Sun's licensees who implement OPEN LOOK GUIs and otherwise comply with Sun's written license agreements.

Federal Acquisitions: Commercial Software—Government Users Subject to Standard License Terms and Conditions.

DOCUMENTATION IS PROVIDED "AS IS" AND ALL EXPRESS OR IMPLIED CONDITIONS, REPRESENTATIONS AND WARRANTIES, INCLUDING ANY IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT, ARE DISCLAIMED, EXCEPT TO THE EXTENT THAT SUCH DISCLAIMERS ARE HELD TO BE LEGALLY INVALID.

Copyright 2001 Sun Microsystems, Inc., 901 San Antonio Road, Palo Alto, CA 94303-4900 Etats-Unis. Tous droits réservés.

Ce produit ou document est distribué avec des licences qui en restreignent l'utilisation, la copie, la distribution, et la décompilation. Aucune partie de ce produit ou document ne peut être reproduite sous aucune forme, par quelque moyen que ce soit, sans l'autorisation préalable et écrite de Sun et de ses bailleurs de licence, s'il y en a. Le logiciel détenu par des tiers, et qui comprend la technologie relative aux polices de caractères, est protégé par un copyright et licencié par des fournisseurs de Sun.

Des parties de ce produit pourront être dérivées des systèmes Berkeley BSD licenciés par l'Université de Californie. UNIX est une marque déposée aux Etats-Unis et dans d'autres pays et licenciée exclusivement par X/Open Company, Ltd.

Sun, Sun Microsystems, le logo Sun, AnswerBook2, docs.sun.com, et Solaris sont des marques de fabrique ou des marques déposées, ou marques de service, de Sun Microsystems, Inc. aux Etats-Unis et dans d'autres pays. Toutes les marques SPARC sont utilisées sous licence et sont des marques de fabrique ou des marques déposées de SPARC International, Inc. aux Etats-Unis et dans d'autres pays. Les produits portant les marques SPARC sont basés sur une architecture développée par Sun Microsystems, Inc.

L'interface d'utilisation graphique OPEN LOOK et Sun™ a été développée par Sun Microsystems, Inc. pour ses utilisateurs et licenciés. Sun reconnaît les efforts de pionniers de Xerox pour la recherche et le développement du concept des interfaces d'utilisation visuelle ou graphique pour l'industrie de l'informatique. Sun détient une licence non exclusive de Xerox sur l'interface d'utilisation graphique Xerox, cette licence couvrant également les licenciés de Sun qui mettent en place l'interface d'utilisation graphique OPEN LOOK et qui en outre se conforment aux licences écrites de Sun.

LA DOCUMENTATION EST FOURNIE "EN L'ETAT" ET TOUTES AUTRES CONDITIONS, DECLARATIONS ET GARANTIES EXPRESSES OU TACITES SONT FORMELLEMENT EXCLUES, DANS LA MESURE AUTORISEE PAR LA LOI APPLICABLE, Y COMPRIS NOTAMMENT TOUTE GARANTIE IMPLICITE RELATIVE A LA QUALITE MARCHANDE, A L'APTITUDE A UNE UTILISATION PARTICULIERE OU A L'ABSENCE DE CONTREFAÇON.

### Contents

### Preface xvii

#### 1. Product Description 1-1

- 1.1 I/O Devices 1-3

- 1.2 System Unit Features 1-3

- 1.3 System Unit Components 1-5

#### 2. SunVTS Overview 2-1

- 2.1 SunVTS Description 2-1

- 2.2 SunVTS Operation 2-2

#### 3. Power-On Self-Test 3-1

- 3.1 POST Overview 3-2

- 3.2 Pre-POST Preparation 3-2

- 3.2.1 Setting Up a Tip Connection 3-3

- 3.2.2 Verifying the Baud Rate 3-4

- 3.3 Initializing POST 3-5

- 3.4 Maximum and Minimum Levels of POST 3-6

- 3.4.1 diag-level Variable Set to max 3-7

- 3.4.2 diag-level Variable Set to min 3-14

|    |       | 3.4.3                                     | POST Progress and Error Reporting 3-18  |  |

|----|-------|-------------------------------------------|-----------------------------------------|--|

|    | 3.5   | Bypass                                    | ing POST 3-21                           |  |

|    | 3.6   | Additional Keyboard Control Commands 3-22 |                                         |  |

|    | 3.7   | System and Keyboard LEDs 3-22             |                                         |  |

|    | 3.8   | Initializ                                 | zing Motherboard POST 3-23              |  |

| 4. | Trout | bleshooting Procedures 4-1                |                                         |  |

|    | 4.1   | Power-                                    | On Failure 4-2                          |  |

|    | 4.2   | Video Output Failure 4-3                  |                                         |  |

|    | 4.3   | Disk Drive or CD-ROM Drive Failure 4-3    |                                         |  |

|    | 4.4   | Power Supply Test 4-5                     |                                         |  |

|    | 4.5   | DIMM Failure 4-7                          |                                         |  |

|    | 4.6   | OpenBoot PROM On-Board Diagnostics 4-8    |                                         |  |

|    |       | 4.6.1                                     | watch-clock 4-9                         |  |

|    |       | 4.6.2                                     | watch-net and watch-net-all $4-9$       |  |

|    |       | 4.6.3                                     | probe-scsi and probe-scsi-all 4-10      |  |

|    |       | 4.6.4                                     | test alias name, device path, -all 4-11 |  |

|    |       | 4.6.5                                     | UPA Graphics Card 4-12                  |  |

|    | 4.7   | OpenB                                     | oot Diagnostics 4-13                    |  |

|    |       | 4.7.1                                     | PCI/Cheerio 4-15                        |  |

|    |       | 4.7.2                                     | EBus DMA/TCR Registers 4-16             |  |

|    |       | 4.7.3                                     | Ethernet 4-16                           |  |

|    |       | 4.7.4                                     | Keyboard 4-17                           |  |

|    |       | 4.7.5                                     | Mouse 4-18                              |  |

|    |       | 4.7.6                                     | Floppy 4-18                             |  |

|    |       | 4.7.7                                     | Parallel Port 4-18                      |  |

|    |       | 4.7.8                                     | Serial Port A 4-19                      |  |

|    |       | 4.7.9                                     | Serial Port B 4-21                      |  |

| 4.7.10 | NVRAM 4-22     |

|--------|----------------|

| 4.7.11 | Audio 4-22     |

| 4.7.12 | SCSI 4-23      |

| 4.7.13 | All Above 4-23 |

### 5. Safety and Tool Requirements 5-1

- 5.1 Safety Requirements 5-2

- 5.2 Symbols 5-2

- 5.3 Safety Precautions 5-3

- 5.3.1 Modification to Equipment 5-3

- 5.3.2 Placement of a Sun Product 5-3

- 5.3.3 Power Cord Connection 5-3

- 5.3.4 Electrostatic Discharge 5-4

- 5.3.5 Lithium Battery 5-4

- 5.4 Tools Required 5-4

### 6. Power On and Off 6-1

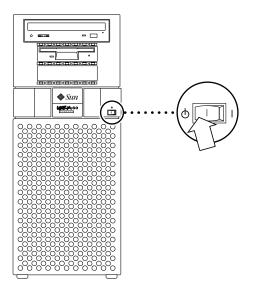

- 6.1 Powering On the System Unit 6-2

- 6.2 Powering Off the System Unit 6-3

### 7. Internal Access 7-1

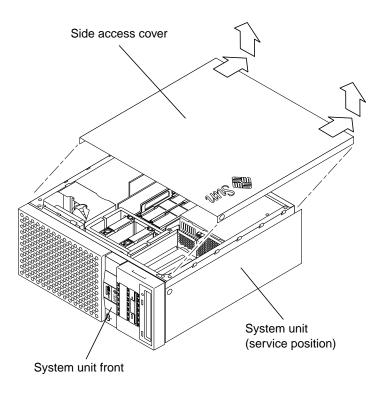

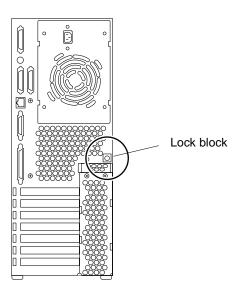

- 7.1 Removing the Side Access Cover 7-2

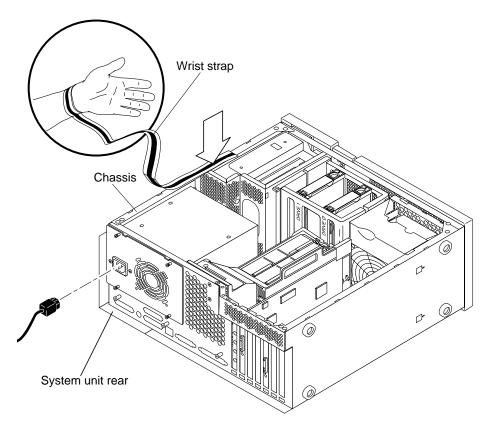

- 7.2 Attaching the Wrist Strap 7-3

- 7.3 Replacing the Side Access Cover 7-4

#### 8. Major Subassemblies 8-1

- 8.1 Power Supply 8-2

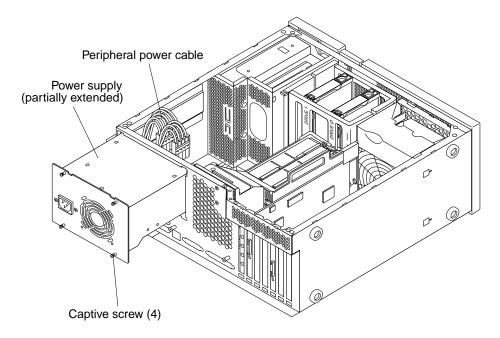

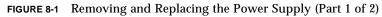

- 8.1.1 Removing the Power Supply 8-2

- 8.1.2 Replacing the Power Supply 8-3

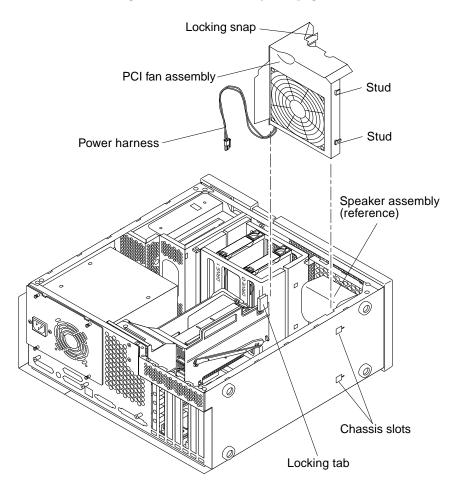

| 8.2 | PCI Fan Assembly | 8-5 |

|-----|------------------|-----|

|-----|------------------|-----|

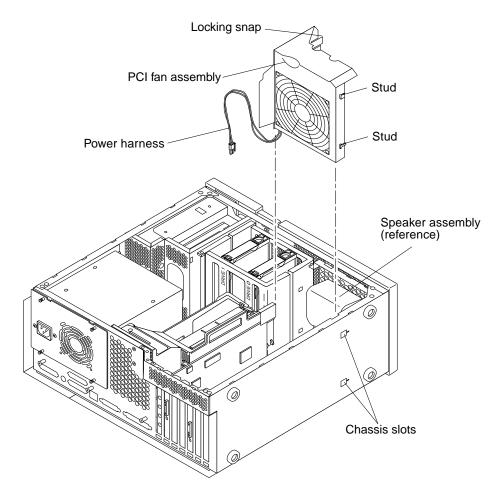

| 8.2.1 Removing the PCI Fan Assembly 8-5 | 8.2.1 | Removing | the PCI Fan | Assembly | 8-5 |

|-----------------------------------------|-------|----------|-------------|----------|-----|

|-----------------------------------------|-------|----------|-------------|----------|-----|

- 8.2.2 Replacing the PCI Fan Assembly 8-6

- 8.3 Hard Drive Bay With SCSI Assembly 8-7

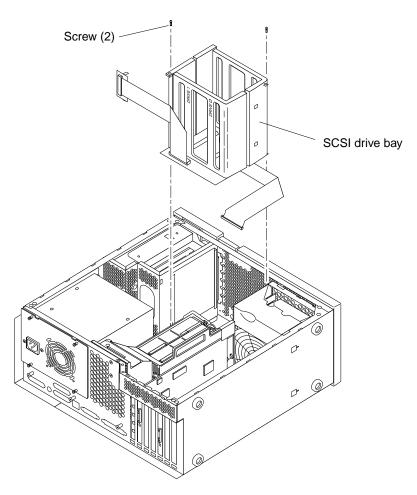

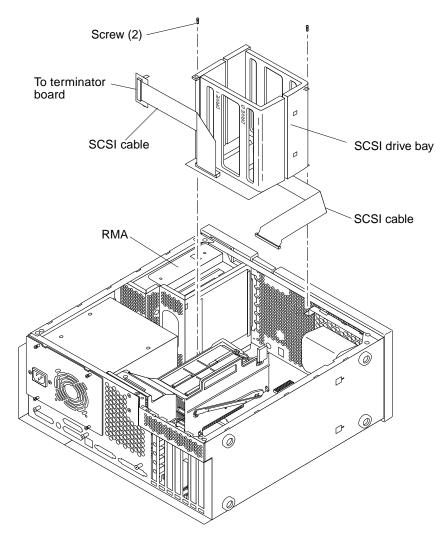

- 8.3.1 Removing the SCSI Drive Bay 8-7

- 8.3.2 Replacing the SCSI Drive Bay 8-9

- 8.4 Cable Assemblies 8-11

- 8.4.1 Removing the Peripheral Power Cable Assembly 8-11

- 8.4.2 Replacing the Peripheral Power Cable Assembly 8-12

- 8.4.3 Removing the Diskette Drive Cable Assembly 8-12

- 8.4.4 Replacing the Diskette Drive Cable Assembly 8-13

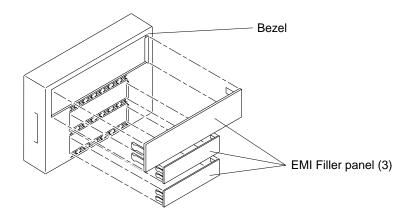

- 8.5 EMI Filler Panels 8-14

- 8.5.1 Removing an EMI Filler Panel 8-14

- 8.5.2 Replacing an EMI Filler Panel 8-15

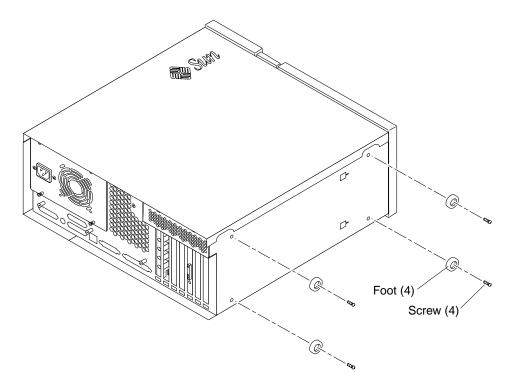

- 8.6 Chassis Foot 8-16

- 8.6.1 Removing the Foot 8-16

- 8.6.2 Replacing the Foot 8-17

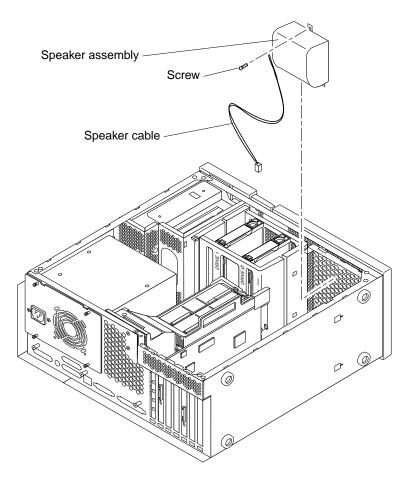

- 8.7 Speaker Assembly 8-17

- 8.7.1 Removing the Speaker Assembly 8-17

- 8.7.2 Replacing the Speaker Assembly 8-18

- 8.8 DC Switch Assembly 8-19

- 8.8.1 Removing the DC Switch Assembly 8-19

- 8.8.2 Replacing the DC Switch Assembly 8-31

- 8.9 CPU Fan Assembly 8-36

- 8.9.1 Removing the CPU Fan Assembly 8-36

- 8.9.2 Replacing the CPU Fan Assembly 8-37

- 8.10 Shroud Assembly 8-38

- 8.10.1 Removing the Shroud Assembly 8-38

- 8.10.2 Replacing the Shroud Assembly 8-39

#### 9. Storage Devices 9-1

- 9.1 Hard Drive 9-2

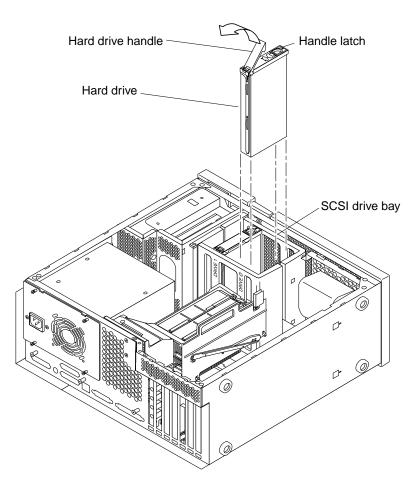

- 9.1.1 Removing a Hard Drive 9-2

- 9.1.2 Replacing a Hard Drive 9-3

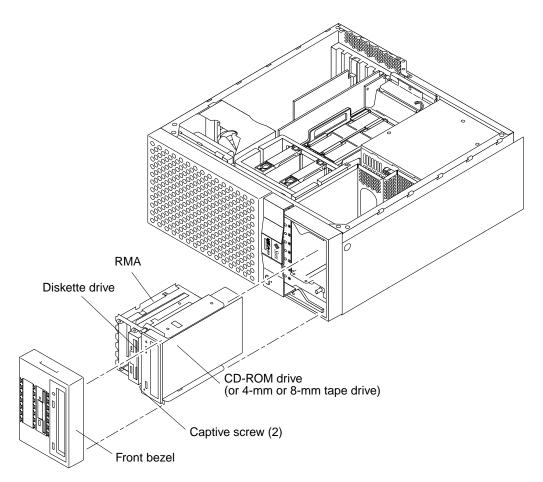

- 9.2 Removable Media Assembly Drive 9-4

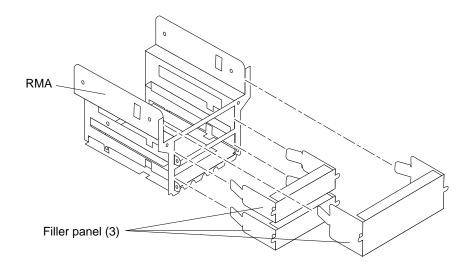

- 9.2.1 Removing the RMA 9-4

- 9.2.2 Removing the CD-ROM Drive or Any X-Option Tape Drive 9-6

- 9.2.3 Replacing the CD-ROM Drive or Any X-Option Tape Drive 9-8

- 9.2.4 Removing the Diskette Drive 9-8

- 9.2.5 Replacing the Diskette Drive 9-9

- 9.2.6 Replacing the RMA 9-9

#### 10. Motherboard and Component Replacement 10-1

- 10.1 CPU Module 10-2

- 10.1.1 Special Considerations for Systems With 450 MHz CPU Modules 10-2

- 10.1.2 Removing the CPU Module 10-2

- 10.1.3 Replacing the CPU Module 10-4

- 10.2 NVRAM/TOD 10-5

- 10.2.1 Removing the NVRAM/TOD 10-5

- 10.2.2 Replacing the NVRAM/TOD 10-6

- 10.3 PCI Card 10-7

- 10.3.1 Removing a PCI Card 10-7

- 10.3.2 Replacing a PCI Card 10-9

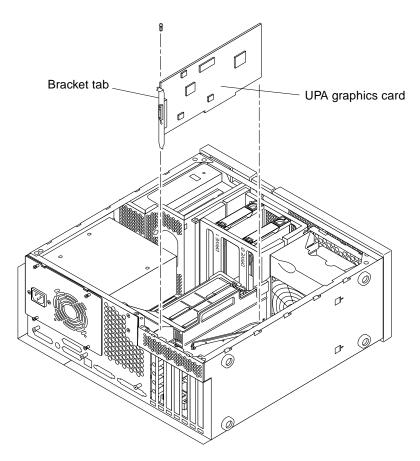

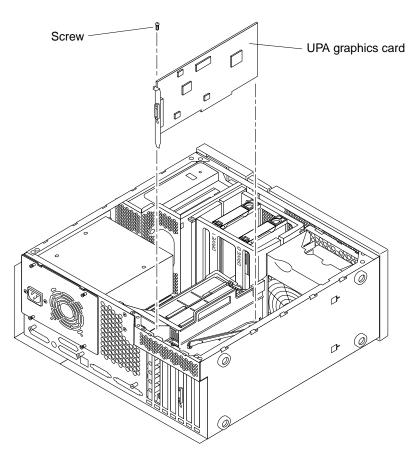

- 10.4 UPA Graphics Card 10-10

- 10.4.1 Removing the UPA Graphics Card 10-10

10.4.2 Replacing the UPA Graphics Card 10-11

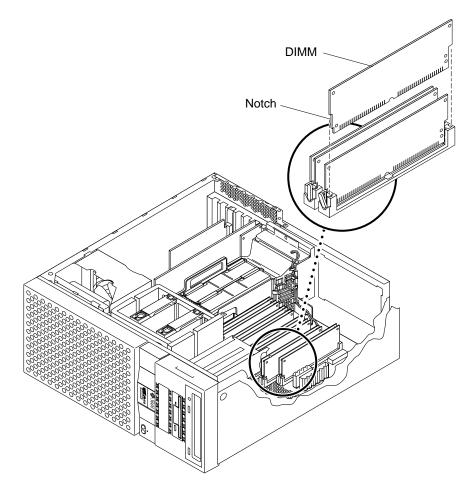

- 10.5 DIMM 10-12

- 10.5.1 Removing a DIMM 10-13

10.5.2 Replacing a DIMM 10-15

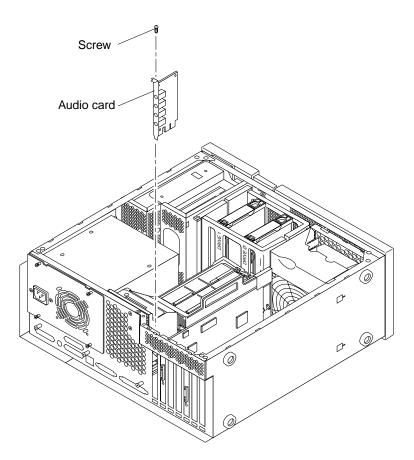

- 10.6 Audio Card 10-16

- 10.6.1 Removing the Audio Card 10-16

10.6.2 Replacing the Audio Card 10-18

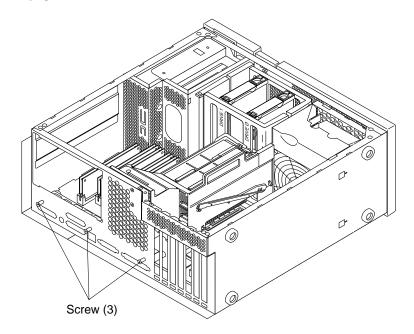

- 10.7 Motherboard 10-19

- 10.7.1 Removing a Motherboard 10-20

- 10.7.2 Replacing a Motherboard 10-23

#### 11. Illustrated Parts List 11-1

#### A. Product Specifications A-1

- A.1 Physical Specifications A-2

- A.2 Electrical Specifications A-2

- A.3 Environmental Requirements A-3

#### **B.** Signal Descriptions B-1

B.1 Keyboard/Mouse and Serial Ports A and B B-2

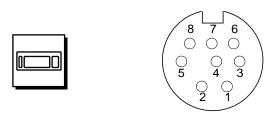

B.1.1 Keyboard/Mouse Connector B-2

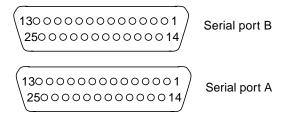

- B.1.2 Serial Port A and B (RS-423/RS-232) Connectors B-3

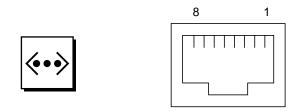

- B.2 Twisted-Pair Ethernet Connector B-5

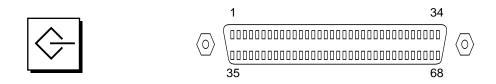

- B.3 UltraSCSI Connector B-6

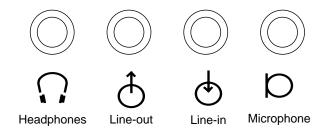

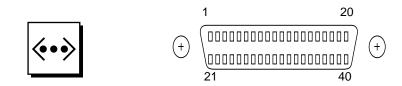

- B.4 Audio Connectors B-10

- B.5 Parallel Port Connector B-11

- B.6 Media Independent Interface Connector B-14

- B.7 UPA Graphics Card Connector B-16

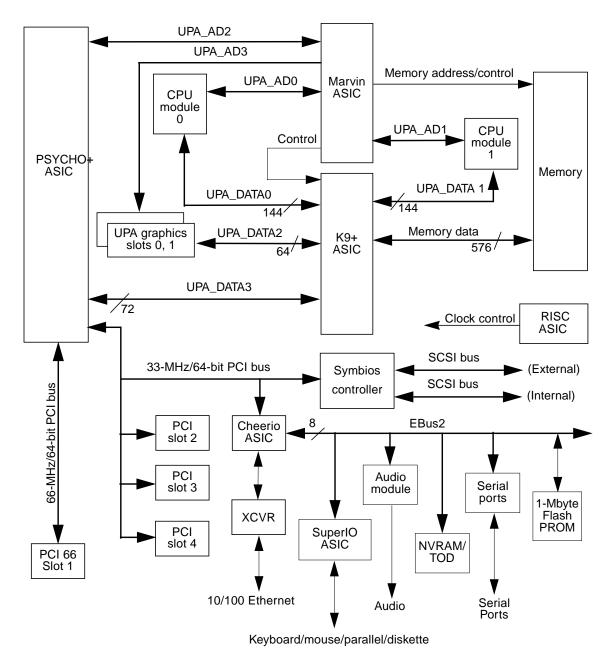

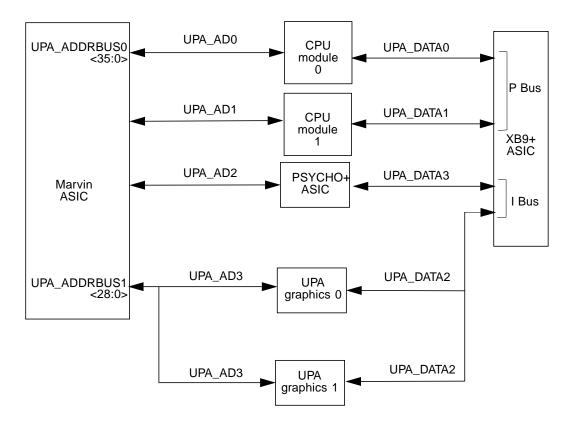

#### C. Functional Description C-1

- C.1 System Unit C-2

- C.1.1 UPA Interconnect C-4

- C.1.2 System Controller C-5

- C.1.3 PCI Bus C-6

- C.1.4 EBus2 Devices C-7

- C.1.5 UltraSPARC II Processor C-8

- C.1.6 Memory System C-9

- C.1.7 Graphics and Imaging C-14

- C.1.8 Peripherals C-15

- C.1.9 Other RMA Storage Device X-Options C-19

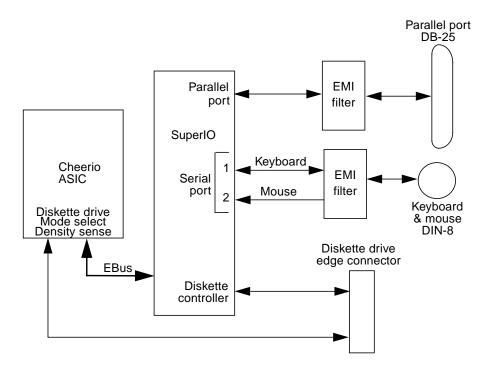

- C.1.10 Keyboard and Mouse, Diskette, and Parallel Port C-19

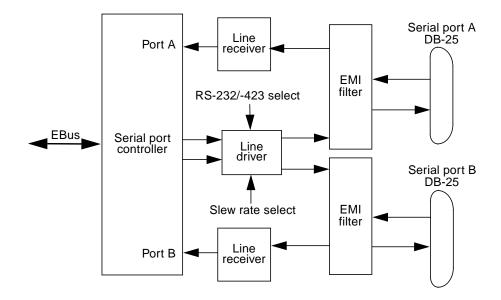

- C.1.11 Serial Port C-22

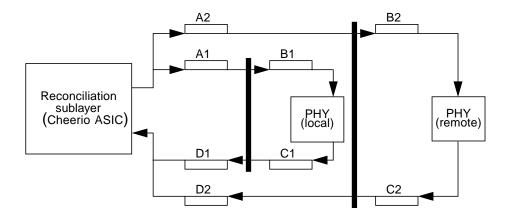

- C.1.12 Ethernet C-24

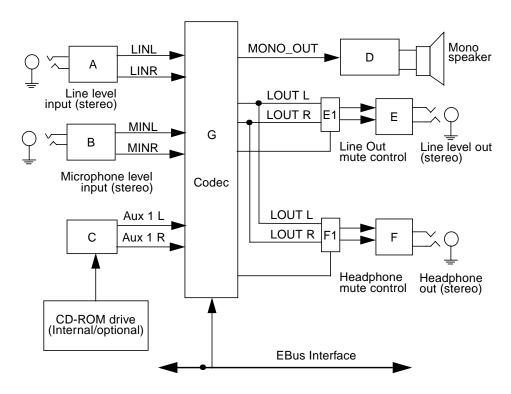

- C.1.13 Audio Card and Connector C-28

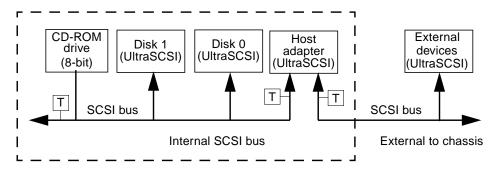

- C.1.14 SCSI C-30

- C.1.15 ASICs C-33

- C.1.16 SuperIO C-36

- C.2 Power Supply C-36

- C.2.1 Control Signals C-37

- C.2.2 Built-In Speaker C-42

- C.2.3 Standard System Facilities C-43

- C.3 Motherboard C-43

- C.4 Jumper Descriptions C-45

- C.4.1 Serial Port Jumpers C-46

- C.4.2 Flash PROM Jumpers C-47

- C.5 Enclosure C-47

- C.5.1 Enclosure Basics C-47

- C.5.2 Enclosure Features C-48

- C.6 Environmental Compliance C-48

- C.7 Agency Compliance C-48

C.8 Energy Star Software Support C-48

Glossary G-1

Index ix-1

## **Figures**

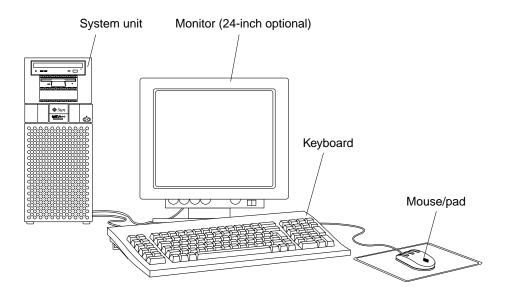

- FIGURE 1-1 Ultra 60 Desktop Workstation 1-2

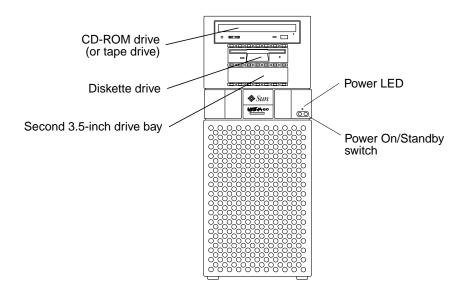

- FIGURE 1-2 System Unit Front View 1-4

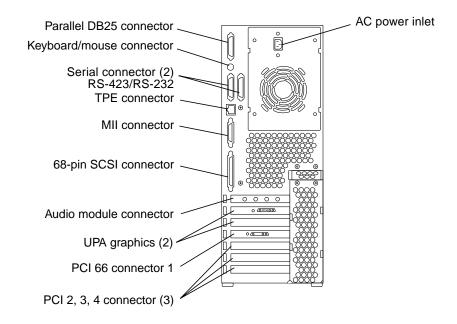

- FIGURE 1-3 System Unit Rear View 1-5

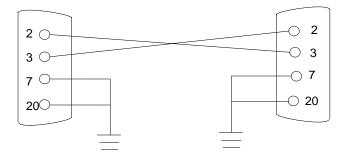

- FIGURE 3-1 Setting Up a TIP Connection 3-3

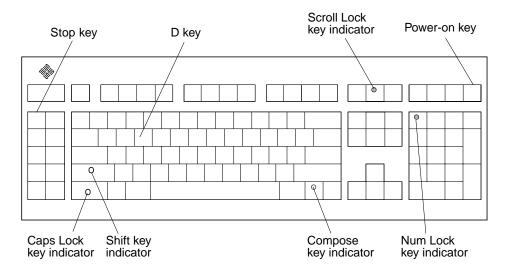

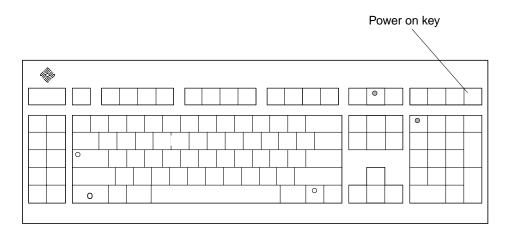

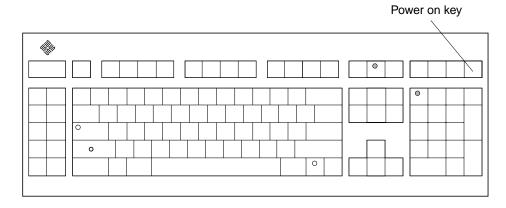

- FIGURE 3-2 Sun Type-5 Keyboard 3-5

- FIGURE 4-1 Power Supply Connector J2901 4-6

- FIGURE 4-2 Power Supply Connector J2902 4-6

- FIGURE 4-3 Power Supply Connector J2903 4-7

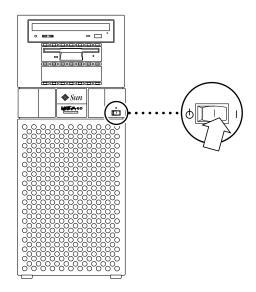

- FIGURE 6-1 System Unit Power-On (Front Panel) 6-2

- FIGURE 6-2 Sun Type-5 Keyboard 6-3

- FIGURE 6-3 System Unit Power-Off (Front Panel) 6-4

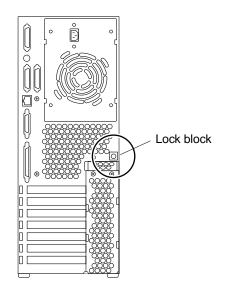

- FIGURE 7-1 Lock Block Location 7-2

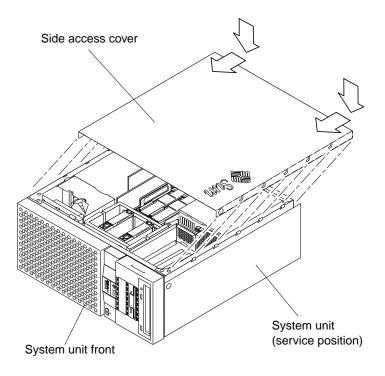

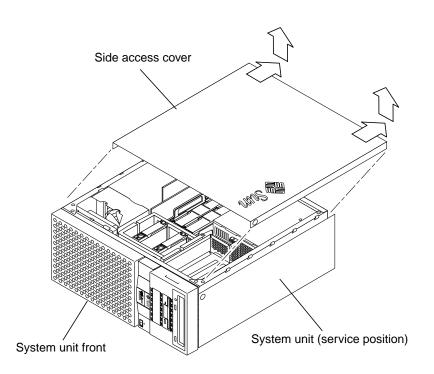

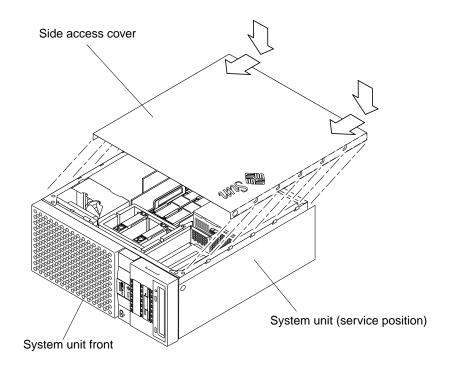

- FIGURE 7-2 Removing the Side Access Cover 7-3

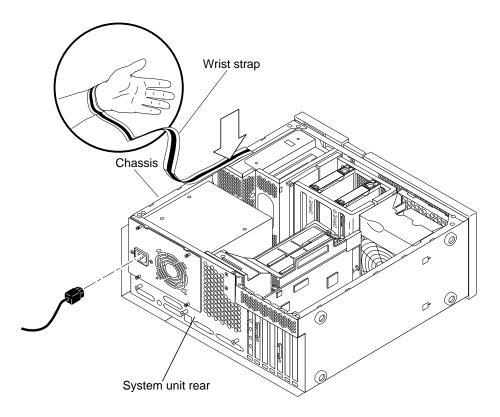

- FIGURE 7-3 Attaching the Wrist Strap to the Chassis 7-4

- FIGURE 7-4 Replacing the Side Access Cover 7-5

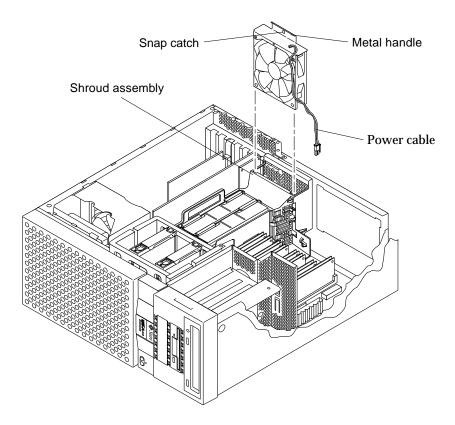

- FIGURE 8-1 Removing and Replacing the Power Supply (Part 1 of 2) 8-3

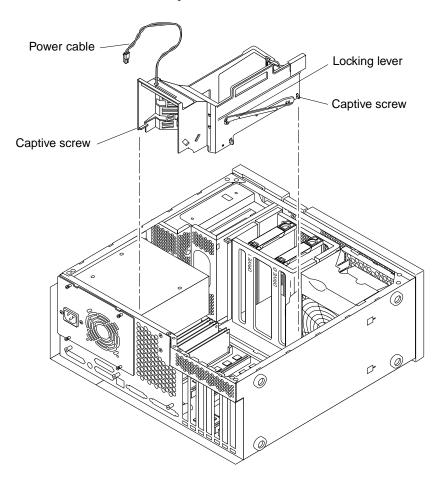

- FIGURE 8-2 Removing and Replacing the Power Supply (Part 2 of 2) 8-4

- FIGURE 8-3 Removing and Replacing the PCI Fan Assembly 8-6

- FIGURE 8-4 Removing and Replacing the SCSI Drive Bay 8-9

- FIGURE 8-5 Removing and Replacing the Bezel EMI Filler Panel 8-15

- FIGURE 8-6 Removing and Replacing the RMA EMI Filler Panel 8-15

- FIGURE 8-7 Removing and Replacing the Chassis Foot 8-16

- FIGURE 8-8 Removing and Replacing the Speaker Assembly 8-18

- FIGURE 8-9 System Unit Power-Off (Front Panel) 8-20

- FIGURE 8-10 Lock Block Location 8-20

- FIGURE 8-11 Removing the Side Access Cover 8-21

- FIGURE 8-12 Attaching the Wrist Strap to the Chassis 8-22

- FIGURE 8-13 Removing and Replacing a PCI Card 8-23

- FIGURE 8-14 Removing and Replacing a UPA Graphics Card 8-24

- FIGURE 8-15 Removing and Replacing the PCI Fan Assembly 8-25

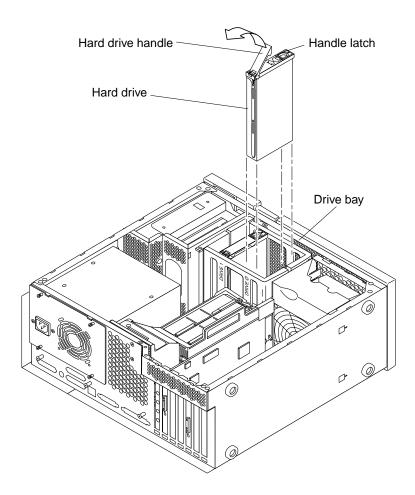

- FIGURE 8-16 Removing and Replacing a Hard Drive 8-26

- FIGURE 8-17 Removing and Replacing the SCSI Drive Bay 8-28

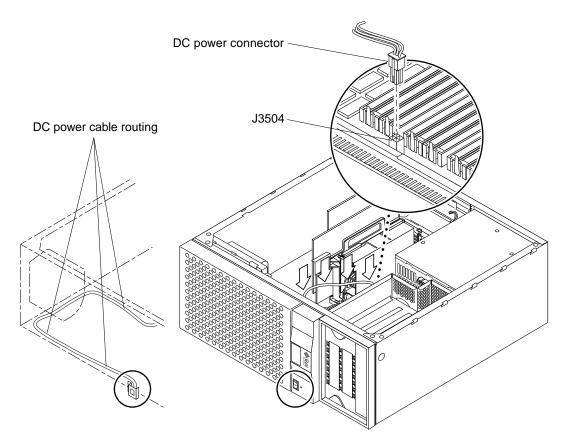

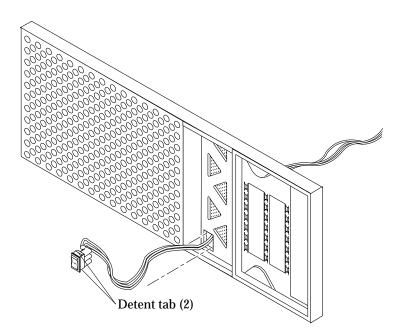

- FIGURE 8-18 DC Switch Assembly Cable Routing 8-29

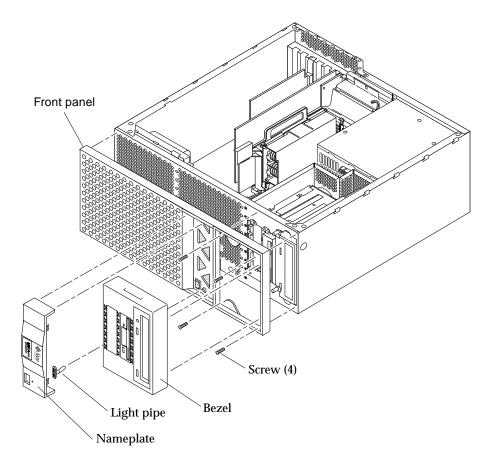

- FIGURE 8-19 Removing and Replacing the Front Panel 8-30

- FIGURE 8-20 Removing and Replacing the Front Panel DC Switch Assembly 8-31

- FIGURE 8-21 Replacing the Side Access Cover 8-34

- FIGURE 8-22 System Unit Power-On (Front Panel) 8-35

- FIGURE 8-23 Sun Type-5 Keyboard 8-35

- FIGURE 8-24 Removing and Replacing the CPU Fan Assembly 8-37

- FIGURE 8-25 Removing and Replacing the Shroud Assembly 8-39

- FIGURE 9-1 Removing and Replacing a Hard Drive 9-3

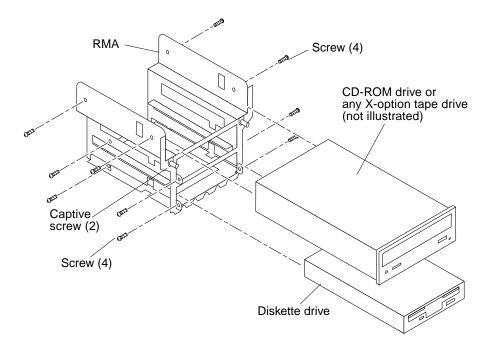

- FIGURE 9-2 Removing and Replacing a RMA Drive (Part 1 of 2) 9-6

- FIGURE 9-3 Removing and Replacing a RMA Drive (Part 2 of 2) 9-7

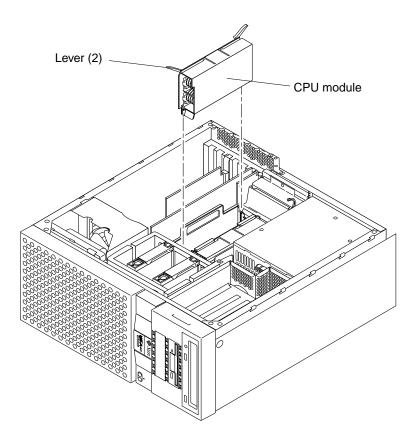

- FIGURE 10-1 Removing and Replacing the CPU Module 10-3

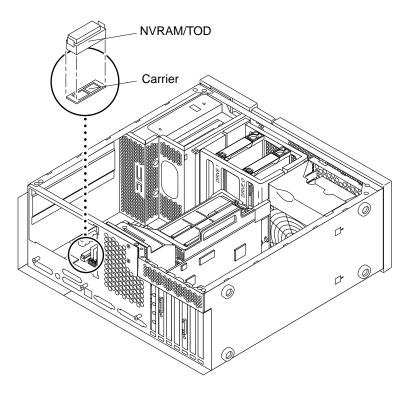

- FIGURE 10-2 Removing and Replacing the NVRAM/TOD 10-6

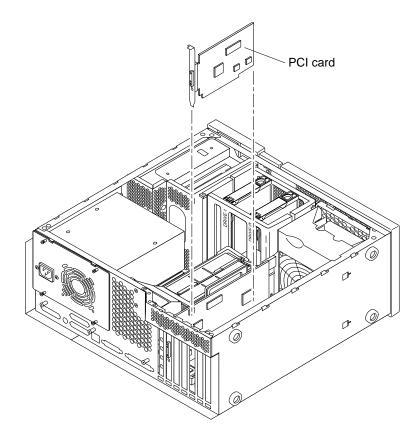

- FIGURE 10-3 Removing and Replacing a PCI Card 10-8

- FIGURE 10-4 Removing and Replacing a UPA Graphics Card 10-11

- FIGURE 10-5 Removing and Replacing a DIMM 10-14

- FIGURE 10-6 Removing and Replacing the Audio Card 10-18

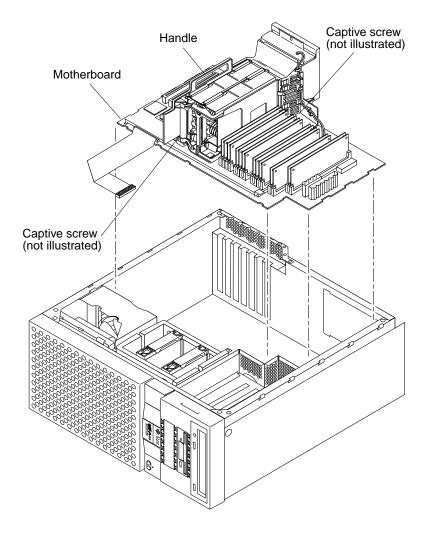

- FIGURE 10-7 Removing and Replacing the Motherboard (Part 1 of 2) 10-21

- FIGURE 10-8 Removing and Replacing the Motherboard (Part 2 of 2) 10-22

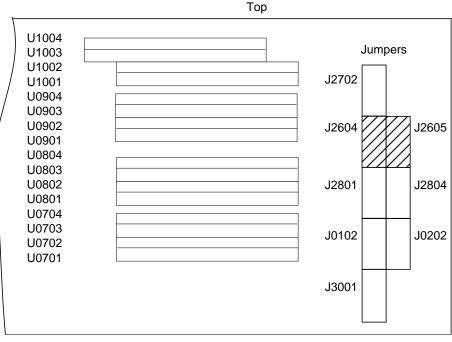

- FIGURE 10-9 Location of the Motherboard Serial Port Jumpers 10-24

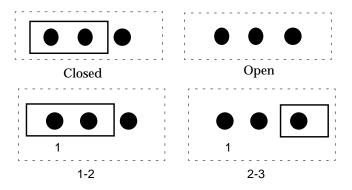

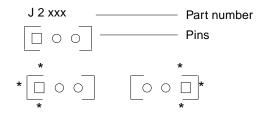

- FIGURE 10-10 Identifying Jumper Pins 10-24

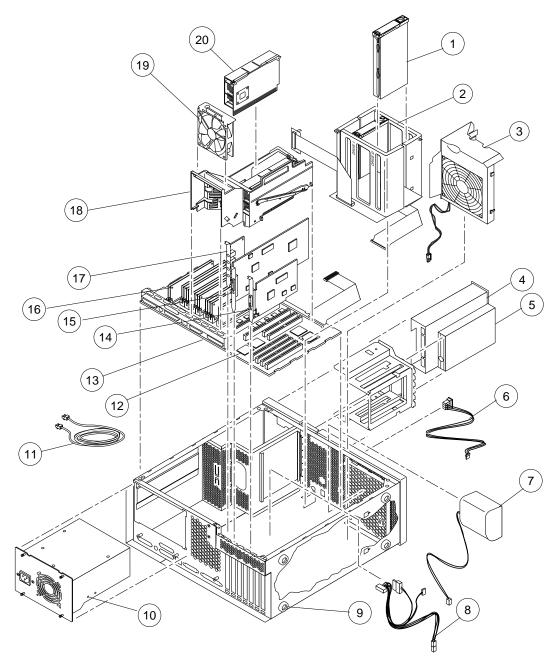

- FIGURE 11-1 System Unit Exploded View 11-2

- FIGURE B-1 Keyboard/Mouse Connector Pin Configuration B-2

- FIGURE B-2 Serial Port A and B Connector Pin Configuration B-3

- FIGURE B-3 TPE Connector Pin Configuration B-6

- FIGURE B-4 UltraSCSI Connector Pin Configuration B-7

- FIGURE B-5 Audio Connector Configuration B-11

- FIGURE B-6 Parallel Port Connector Pin Configuration B-12

- FIGURE B-7 MII Connector Pin Configuration B-14

- FIGURE B-8 UPA Graphics Card Connector Pin Configuration B-16

- FIGURE C-1 Ultra 60 System Unit Functional Block Diagram C-3

- FIGURE C-2 UPA Address and Data Buses Functional Block Diagram C-5

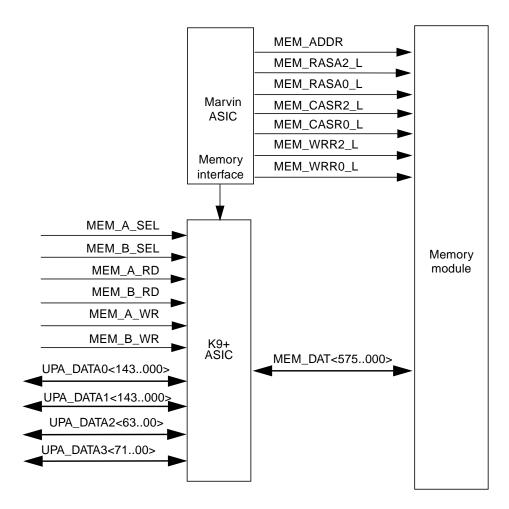

- FIGURE C-3 Memory System Functional Block Diagram C-10

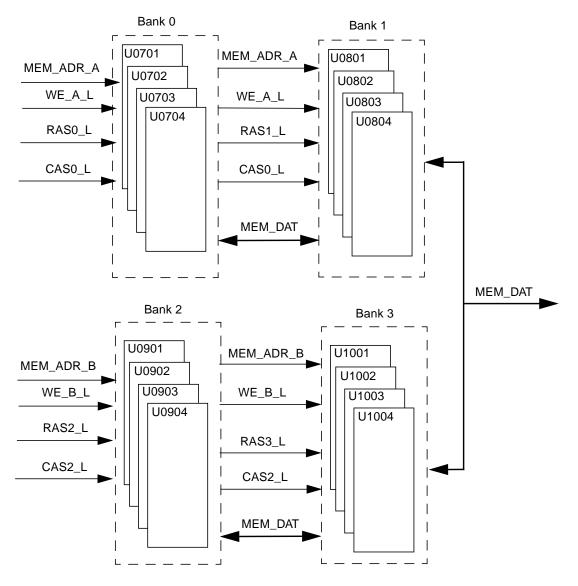

- FIGURE C-4 Memory Module Functional Block Diagram C-11

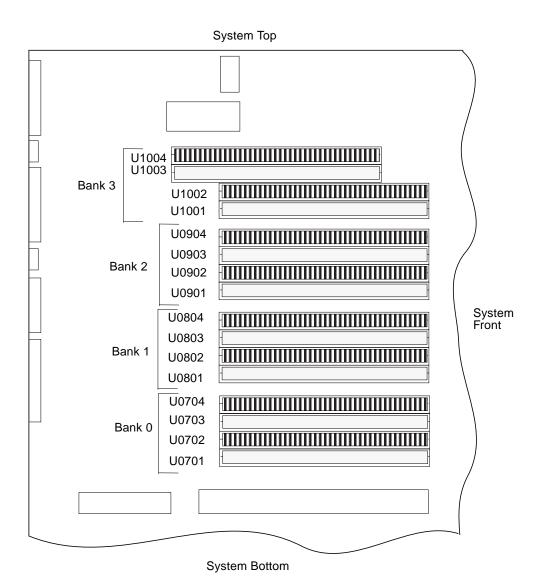

- FIGURE C-5 DIMM Mapping C-12

- FIGURE C-6 Keyboard and Mouse, Diskette, and Parallel Port Functional Block Diagram C-20

- FIGURE C-7 Serial Port Functional Block Diagram C-23

- FIGURE C-8 MII Port Timing Model C-27

- FIGURE C-9 Audio Card Functional Block Diagram C-29

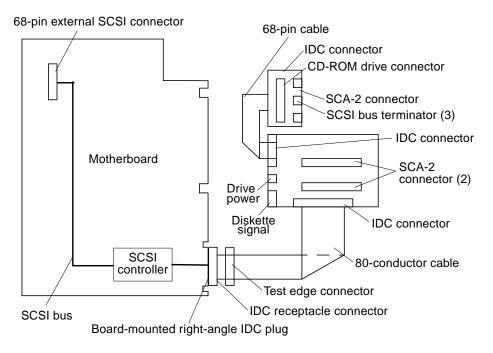

- FIGURE C-10 Configuration for the SCSI Bus  $C\mathchar`-30$

- FIGURE C-11 SCSI Subassembly Functional Block Diagram C-32

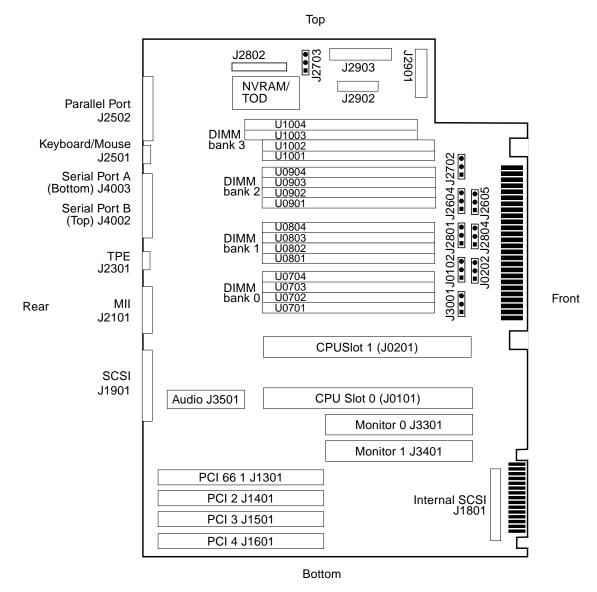

- FIGURE C-12 System Unit Motherboard Functional Block Diagram C-44

- FIGURE C-13 Selected Jumper Settings C-45

- FIGURE C-14 Identifying Jumper Pins C-45

### **Tables**

- TABLE 1-1 Supported I/O Devices 1-3

- TABLE 1-2 System Unit Replaceable Components 1-6

- TABLE 2-1 SunVTS Documentation 2-2

- TABLE 3-1 Diag-Level Switch Settings 3-2

- TABLE 3-2 Keyboard LED Patterns 3-21

- TABLE 4-1 Internal Drives Identification 4-4

- TABLE 4-2 Power Supply Connector J2901 Pin Description 4-6

- TABLE 4-3 Power Supply Connector J2902 Pin Description 4-6

- TABLE 4-4 Power Supply Connector J2903 Pin Description 4-7

- TABLE 4-5 DIMM Physical Memory Address 4-8

- TABLE 4-6 Selected OBP On-Board Diagnostic Tests 4-12

- TABLE 10-1 DIMM Bank and Bank Quad 10-13

- TABLE 10-2 Serial Port Jumper Settings 10-23

- TABLE 11-1 System Unit Replaceable Components 11-3

- TABLE A-1 System Unit Physical Specifications A-2

- TABLE A-2 Electrical Specifications A-2

- TABLE A-3 Environmental Requirements A-3

- TABLE B-1 Keyboard/Mouse Connector Pin Assignments B-2

- TABLE B-2 Serial Port A and B Connector Pin Assignments B-3

- TABLE B-3 TPE Connector Pin Assignments B-6

- TABLE B-4 UltraSCSI Connector Pin Assignments B-7

- TABLE B-5 Audio Connector Line Assignment B-11

- TABLE B-6 Parallel Port Connector Pin Assignments B-12

- TABLE B-7 MII Connector Pin Assignments B-14

- TABLE B-8 UPA Graphics Card Connector Pin Assignments B-16

- TABLE C-1 UPA Port Identification Assignments C-4

- TABLE C-2 DIMM Bank-to-U-Number Mapping C-13

- TABLE C-3 IL = 0, DIMM Bank-to-Physical Address Mapping C-14

- TABLE C-4 Diskette Drive Signals and Functions C-17

- TABLE C-5 Supported Hard Drives C-18

- TABLE C-6 Audio Card Features C-28

- TABLE C-7 Supported Target Devices C-31

- TABLE C-8 Power Supply Output Values C-36

- TABLE C-9 Power Supply Control Signal C-37

- TABLE C-10 300-MHz (3.3-ns) CPU Module(s) Power Estimate C-40

- TABLE C-11 PCI Card (5 Vdc) Power Estimate C-40

- TABLE C-12 PCI Card (3.3 Vdc) Power Estimate C-41

- TABLE C-13 Memory Subsystem Power Estimate C-41

- TABLE C-14 Mass Storage Device Power Estimates C-41

- TABLE C-15 Built-In Speaker Specifications C-42

- TABLE C-16 Serial Port Jumper Settings C-46

- TABLE C-17 Flash PROM Jumper Settings C-47

### Preface

The *Sun Ultra 60 Service Manual* provides detailed procedures that describe the removal and replacement of replaceable parts in the Ultra<sup>™</sup> 60 computer (system unit). The service manual also includes information about the use and maintenance of the system unit. This book is written for technicians, system administrators, authorized service providers (ASPs), and advanced computer system end users who have experience troubleshooting and replacing hardware.

### How This Book Is Organized

This document is organized into chapters and appendices as listed in TABLE P-1. A glossary and an index is also included.

| Chapter Number/Title                      | Content Description                                                                                 |

|-------------------------------------------|-----------------------------------------------------------------------------------------------------|

| Chapter 1, "Product Description"          | Describes the major components of the system unit.                                                  |

| Chapter 2, "SunVTS Overview"              | Describes the execution of individual tests for verifying hardware configuration and functionality. |

| Chapter 3, "Power-On Self-Test"           | Describes the execution of POST and provides examples of POST output patterns.                      |

| Chapter 4, "Troubleshooting Procedures"   | Provides troubleshooting advice and suggested corrective actions for hardware problems.             |

| Chapter 5, "Safety and Tool Requirements" | Explains how to work safely when servicing the system unit.                                         |

TABLE P-1

Document Organization

| Chapter Number/Title                                | Content Description                                                                                                                                                                                                 |

|-----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chapter 6, "Power On and Off"                       | Provides step-by-step procedures to power<br>on and power off the system unit.                                                                                                                                      |

| Chapter 7, "Internal Access"                        | Provides step-by-step procedures to remove<br>the side access panel, attach the wrist strap,<br>and replace the side access panel.                                                                                  |

| Chapter 8, "Major Subassemblies"                    | Provides step-by-step procedures to remove and replace major subassemblies.                                                                                                                                         |

| Chapter 9, "Storage Devices"                        | Provides step-by-step procedures to remove and replace storage devices.                                                                                                                                             |

| Chapter 10, "Motherboard and Component Replacement" | Provides step-by-step procedures to remove<br>and replace the motherboard, and various<br>components associated with motherboard<br>operation.                                                                      |

| Chapter 11, "Illustrated Parts List"                | Lists replaceable parts for the system unit.                                                                                                                                                                        |

| Appendix A, "Product Specifications"                | Provides product specifications, system<br>requirements about power and environment,<br>system unit dimensions, weight, memory<br>mapping, and peripheral component<br>interconnect (PCI) card slot specifications. |

| Appendix B, "Signal Descriptions"                   | Provides signal descriptions.                                                                                                                                                                                       |

| Appendix C, "Functional Description"                | Provides functional descriptions for the system unit.                                                                                                                                                               |

| Glossary                                            | Provides a listing of acronyms, terms, and definitions.                                                                                                                                                             |

| Index                                               | Provides a quick reference to specific topics.                                                                                                                                                                      |

TABLE P-1

Document Organization (Continued)

## **UNIX** Commands

This document may not contain information on basic  $\textsc{UNIX}^{\texttt{B}}$  commands and procedures.

See one or more of the following for this information:

- Solaris 2.x Handbook for SMCC Peripherals.

- AnswerBook<sup>™</sup> online documentation for the Solaris<sup>™</sup> 2.x software environment.

- Other software documentation that you received with your system.

# **Typographic Conventions**

| Typeface or Symbol | Meaning                                                                                                                           | Examples                                                                                                                                                                     |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AaBbCc123          | The names of commands,<br>files, and directories;<br>on-screen computer output.                                                   | Edit your .login file.<br>Use ls -a to list all files.<br>% You have mail.                                                                                                   |

| AaBbCc123          | What you type, when contrasted with on-screen computer output.                                                                    | % <b>su</b><br>Password:                                                                                                                                                     |

| AaBbCc123          | Book titles, new words or<br>terms, words to be<br>emphasized.<br>Command-line variable;<br>replace with a real name or<br>value. | Read Chapter 6 in the User's<br>Guide.<br>These are called <i>class</i><br>options.<br>You <i>must</i> be root to do this.<br>To delete a file, type rm<br><i>filename</i> . |

TABLE P-2

Typographic Conventions

## **Shell Prompts**

TABLE P-3Shell Prompts

| Shell                                 | Prompt        |

|---------------------------------------|---------------|

| C shell                               | machine_name% |

| C shell superuser                     | machine_name# |

| Bourne shell and Korn shell           | \$            |

| Bourne shell and Korn shell superuser | #             |

# **Related Documents**

| TABLE P-4 | Related Documents |  |

|-----------|-------------------|--|

|           |                   |  |

| Application       | Title                                                                                      | Part Number |

|-------------------|--------------------------------------------------------------------------------------------|-------------|

| Configuration     | Sun Ultra 60 System Reference<br>Manual                                                    | 802-4147    |

| Configuration     | Solaris Handbook for SMCC<br>Peripherals                                                   | 802-7675    |

| Diagnostics       | SunVTS 2.0 User's Guide                                                                    | 802-5331    |

| Diagnostics       | SunVTS 2.0 Test Reference<br>Manual                                                        | 802-5330    |

| Diagnostics       | SunVTS 2.0 Quick Reference<br>Card                                                         | 802-5329    |

| Installation      | 14-Gbyte, 8-mm Tape Drive<br>Installation Manual                                           | 802-1849    |

| Installation      | Creator Frame Buffer<br>Installation Guide                                                 | 802-6682    |

| Installation/user | 12-24 Gbyte 4-mm DDS-3<br>Tape Drive Installation and<br>User's Guide                      | 802-7791    |

| Installation      | 5.25" Fast/Wide Differential<br>SCSI Disk Drive Installation<br>Manual                     | 802-1653    |

| Installation/user | SunCD 12 Installation and User's Guide                                                     | 805-0940    |

| Specification     | Manual Eject Diskette Drive<br>Specifications                                              | 805-1133    |

| Specification     | 17-Inch Entry, 17-Inch<br>Premium, and 20-Inch<br>Premium Color Monitors<br>Specifications | 802-6168    |

| Specification     | 4.2-Gbyte 7200-RPM Disk<br>Drive Specifications                                            | 802-7744    |

| Specification     | 9-Gbyte 7200-RPM Disk Drive<br>Specifications                                              | 802-7745    |

| Specification     | SunCD 4 Drive Specifications                                                               | 802-4157    |

| Application   | Title                                                                 | Part Number |

|---------------|-----------------------------------------------------------------------|-------------|

| Specification | 8-mm Tape Drive Specifications                                        | 802-5775    |

| Specification | 4-mm, DDS-2 Tape Drive<br>Specifications                              | 802-7790    |

| Specification | Manual Eject Diskette Drive<br>Specifications                         | 805-1133    |

| User          | 24-Inch Premium<br>(22.5-inch Viewable) Color<br>Monitor Guide        | 875-1799    |

| User          | 14-Gbyte, 8-mm Tape Drive<br>User's Guide                             | 802-1850    |

| User          | SBus Wide Intelligent<br>UltraSCSI Differential Host<br>Adapter Guide | 802-7748    |

TABLE P-4

Related Documents (Continued)

## **Accessing Sun Documentation Online**

A broad selection of Sun system documentation is located at:

http://www.sun.com/products-n-solutions/hardware/docs

A complete set of Solaris documentation and many other titles are located at:

http://docs.sun.com

## **Ordering Sun Documentation**

Fatbrain.com, an Internet professional bookstore, stocks select product documentation from Sun Microsystems, Inc.

For a list of documents and how to order them, visit the Sun Documentation Center on Fatbrain.com at:

http://www.fatbrain.com/documentation/sun

## Sun Welcomes Your Comments

Sun is interested in improving its documentation and welcomes your comments and suggestions. You can email your comments to Sun at:

docfeedback@sun.com

Please include the part number (805-1709-12) of your document in the subject line of your email.

## **Product Description**

The Ultra 60 desktop workstation is a multiprocessor device that uses the family of UltraSPARC<sup>™</sup> processors. It supports high-performance processing and high-performance graphics. FIGURE 1-1 illustrates the Ultra 60 desktop workstation. Enclosed within a minitower enclosure, the Ultra 60 desktop workstation provides the following:

- Power and cooling requirements for a high-performance processor and graphic function

- Modular internal design

- Improved disk, system, memory, and I/O performance and capacities

- Dual-head UltraSPARC port architecture (UPA) graphics capability

- High-performance peripheral component interconnect (PCI) I/O expansion with comparable options to existing SBus options

This chapter contains the following topics:

- I/O Devices—page 1-3

- System Unit Features—page 1-3

- System Unit Components—page 1-5

FIGURE 1-1 Ultra 60 Desktop Workstation

## 1.1 I/O Devices

The Ultra 60 desktop workstation uses the I/O devices listed in TABLE 1-1.

| TABLE 1-1 | Supported I/O D | <b>Pevices</b> |

|-----------|-----------------|----------------|

|-----------|-----------------|----------------|

| I/O Devices                      | Description                                                              |  |

|----------------------------------|--------------------------------------------------------------------------|--|

| 20-inch (51-cm)<br>color monitor | 1152 x 900 resolution, 76- or 66-Hz refresh rate, 84 dots per inch (dpi) |  |

|                                  | 1280 x 1024 resolution, 76- or 66-Hz refresh rate, 93 dpi                |  |

|                                  | 960 x 680 resolution, 112-Hz refresh rate, 70 dpi                        |  |

| 24-inch (61-cm)<br>color monitor | 1920 x 1200 resolution, 70-Hz refresh rate, 103 dpi                      |  |

|                                  | 1600 x 1000 resolution, 76- or 66-Hz refresh rate, 86 dpi                |  |

|                                  | 1400 x 900 resolution, 76-Hz refresh rate, 77 dpi                        |  |

|                                  | 1280 x 800 resolution, 76-Hz refresh rate, 69 dpi                        |  |

| Microphone <sup>1</sup>          | SunMicrophone <sup>™</sup> II                                            |  |

| Keyboard                         | Sun Type-5; AT 101 or UNIX layout available                              |  |

| Opto-mechanical<br>mouse         | Optomechanical, 3-button                                                 |  |

1. No longer ships with system, optional

## 1.2 System Unit Features

System unit components are housed in a tower configuration enclosure. Overall enclosure dimensions (width x depth x height) are 7.50 inches (19.0 cm) x 19.60 inches (49.8 cm) x 17.70 inches (45.0 cm). System unit electronics are contained on a single printed circuit board (motherboard). The motherboard contains the CPU modules, memory, system control application specific integrated circuits (ASICs), and I/O ASICs.

FIGURE 1-2 illustrates the system unit front view. FIGURE 1-3 illustrates the system unit rear view. System unit electronics and peripherals contain (or may be upgraded to contain) the following features:

- Tower enclosure with 350-watt power supply.

- Support for modular UltraSPARC II processor with up to a 4-megabyte (Mbyte) Ecache and system operating frequencies from 100 megahertz (MHz) to 400 MHz.

- 83.3-MHz to 120-MHz UPA coherent memory interconnect.

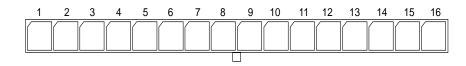

- Use of dual in-line memory modules (DIMMs). Each group of four DIMM slots accepts 16-, 32-, 64-, or 128-Mbyte DIMM modules. Populating with four identical capacity DIMMs enables the memory controller for optimal system performance. There are a total of 16 DIMM slots.

- Four PCI slots: three 33-MHz, 64-bit or 32-bit, 5 Vdc slots; one 66-MHz or 33-MHz, 64-bit or 32-bit, 3.3 Vdc slot

- Two UPA graphics slots.

- 10-/100-megabits per second Ethernet.

- 40-Mbytes per second UltraSCSI.

- Two DB25 serial ports (synchronous and asynchronous protocols).

- Centronics-compatible parallel port interface with extended capability port (ECP) support.

- Modular audio interface.

FIGURE 1-2 System Unit Front View

FIGURE 1-3 System Unit Rear View

## 1.3 System Unit Components

TABLE 1-2 lists the system unit components by part number. A brief description of each listed component is also provided.

**Note** – Removal and replacement of selected system unit components are also illustrated with photographs and audio/visual instructions on the *Sun Ultra 60 ShowMe How Multimedia Documentation*, part number 704-5886.

## **Note** – Consult your authorized Sun sales representative or service provider to confirm a part number prior to ordering a replacement part.

| TABLE 1-2         System Unit Replaceable Components |                                                        |  |  |

|------------------------------------------------------|--------------------------------------------------------|--|--|

| Component                                            | Description                                            |  |  |

| Motherboard                                          | System board                                           |  |  |

| Hard drive bay with SCSI                             | Mechanical hard drive housing                          |  |  |

| 4.2-Gbyte SCSI assembly                              | Hard disk drive, 3.5-inch x 1.0-inch                   |  |  |

| 9.1-Gbyte SCSI assembly                              | Hard disk drive, 3.5-inch x 1.6-inch                   |  |  |

| PCI fan assembly                                     | PCI fan                                                |  |  |

| Shroud assembly                                      | Two-CPU shroud assembly                                |  |  |

| Fan assembly                                         | CPU fan                                                |  |  |

| CPU module                                           | 300-MHz, 2-Mbyte external cache                        |  |  |

| Graphics card                                        | Vertical, single buffer UPA graphics card              |  |  |

| Graphics card                                        | Vertical, double buffer plus Z (DBZ) UPA graphics card |  |  |

| Power supply                                         | Power supply, 350 watts                                |  |  |

| PCI card                                             | Generic                                                |  |  |

| Audio module                                         | Audio applications, 16-bit audio, 8 kHz to 48 kHz      |  |  |

| Speaker assembly                                     | Speaker                                                |  |  |

| Peripheral cable                                     | Peripheral cable                                       |  |  |

| Diskette drive cable                                 | Diskette drive cable                                   |  |  |

| Manual eject floppy                                  | Diskette drive, 3.5-inch, MS-DOS compatible            |  |  |

| EMI filler panel                                     | CD-ROM drive filler panel                              |  |  |

| EMI filler panel                                     | Diskette drive filler panel                            |  |  |

| 16-Mbyte DIMM                                        | 60-ns, 16-Mbyte DIMM                                   |  |  |

TABLE 1-2

System Unit Replaceable Components

| Component              | Description                               |

|------------------------|-------------------------------------------|

| 32-Mbyte DIMM          | 60-ns, 32-Mbyte DIMM                      |

| 64-Mbyte DIMM          | 60-ns, 64-Mbyte DIMM                      |

| 128-Mbyte DIMM         | 60-ns, 128-Mbyte DIMM                     |

| NVRAM/TOD              | Time of day, 48T59, with carrier          |

| CD-ROM drive           | 12X-speed CD-ROM drive, 644-Mbyte SunCD™  |

| 4-mm tape drive        | 4-Gbyte/8-Gbyte, 4-mm tape drive, DDS-2   |

| 4-mm tape drive        | 12-Gbyte/24-Gbyte, 4-mm tape drive, DDS-3 |

| 8-mm tape drive        | 14-Gbyte, 8-mm tape drive                 |

| TPE cable (category 5) | Twisted-pair Ethernet cable               |

| DC switch assembly     | DC switch assembly                        |

### TABLE 1-2 System Unit Replaceable Components (Continued)

### **SunVTS** Overview

This chapter contains an overview of the SunVTS<sup>™</sup> diagnostic tool.

This chapter contains the following topics:

- SunVTS Description—page 2-1

- SunVTS Operation—page 2-2

### 2.1 SunVTS Description

The SunVTS software executes multiple diagnostic hardware tests from a single user interface. SunVTS verifies the configuration, functionality, and reliability of most hardware controllers and devices.

The SunVTS software can be used in both the Common Desktop Environment (CDE) and the OPEN LOOK graphical user interface (GUI) environments, or from a TTY interface.

Within the CDE and OPEN LOOK GUI environments, test parameters can be set quickly and easily by pointing and clicking a mouse button.

With a TTY interface, the SunVTS software is used from a terminal or modem attached to a serial port. Data is input through the keyboard, rather than with a mouse, and only one screen of information is displayed at a time.

## 2.2 SunVTS Operation

TABLE 2-1 lists the documentation for the SunVTS software. These documents are available on the *Solaris on Sun Hardware AnswerBook*, which is on the *SMCC Updates* for the Solaris release.

| Title                        | Part Number | Description                                                                                                    |

|------------------------------|-------------|----------------------------------------------------------------------------------------------------------------|

| SunVTS User's Guide          | 802-7299    | Describes the SunVTS environment;<br>starting and controlling various user<br>interfaces; feature descriptions |

| SunVTS Test Reference Manual | 802-7300    | Describes each SunVTS test; provides various test options and command line arguments                           |

| SunVTS Quick Reference Card  | 802-7301    | Provides overview of vtsui interface<br>features                                                               |

TABLE 2-1

SunVTS Documentation

## **Power-On Self-Test**

This chapter describes how to initiate power-on self-test (POST) diagnostics. The examples given in this chapter are representative, details of actual test results may be different, depending on system configurations.

This chapter contains the following topics:

- POST Overview—page 3-2

- Pre-POST Preparation—page 3-2

- Initializing POST—page 3-5

- Maximum and Minimum Levels of POST—page 3-6

- POST Progress and Error Reporting—page 3-18

- Bypassing POST—page 3-21

- Additional Keyboard Control Commands—page 3-22

- System and Keyboard LEDs—page 3-22

- Initializing Motherboard POST—page 3-23

## 3.1 POST Overview

POST is useful in determining if a portion of the system unit has failed and should be replaced. POST detects approximately 95 percent of system unit faults and is located in the system board OpenBoot<sup>™</sup> PROM (OBP). The setting of two NVRAM variables, the diag-switch? and the diag-level flag, determine if POST is executed. TABLE 3-1 lists the diag-switch? and diag-level flag settings for disabling POST (off), enabling POST maximum (max), or enabling POST minimum (min).

| TABLE 3-1 | Diag-Level | Switch | Settings |

|-----------|------------|--------|----------|

|-----------|------------|--------|----------|

| Diag-Level Setting | POST<br>Initialization | Serial Port A<br>I/O | Serial Port A<br>Error Output | Diag-Switch?<br>Setting |

|--------------------|------------------------|----------------------|-------------------------------|-------------------------|

| Off                | No                     | N/A                  | N/A                           | N/A                     |

| Max                | Yes (power-on)         | Enabled              | Enabled                       | True                    |

| Min                | Yes (power-on)         | Disabled             | Enabled                       | True                    |

## 3.2 **Pre-POST Preparation**

Pre-POST preparation includes:

- Setting up a tip connection to another workstation or terminal to view POST progress and error messages. See Section 3.2.1, "Setting Up a Tip Connection" on page 3-3.

- Verifying baud rates between a workstation and a monitor or a workstation and a terminal. See Section 3.2.2, "Verifying the Baud Rate" on page 3-4.

If a terminal or a monitor is not connected to serial port A (default port) of a workstation or server to be tested, the keyboard LEDs are used to determine error conditions. See Section 3.7, "System and Keyboard LEDs" on page 3-22

### 3.2.1 Setting Up a Tip Connection

A tip connection enables a remote shell window to be used as a terminal to display test data of a system being tested. Serial port A or serial port B of a tested system unit is used to establish the tip connection between the system unit being tested and another Sun workstation monitor or TTY-type terminal. The tip connection is used in a SunOS<sup>TM</sup> window and provides features to help with the OBP.

To set up a tip connection:

1. See FIGURE 3-1. Connect serial port A of the system being tested to serial port B of another Sun workstation using a serial null modem cable (connect cable pins 2-3, 3-2, 7-20, and 20-7).

FIGURE 3-1 Setting Up a TIP Connection

2. At the other Sun workstation, check the /etc/remote file by changing to the /etc directory and then editing the remote file:

hardwire:/ dv=/dev/term/b:br#9600:el=^C^S^Q^U^D:ie=%\$:oe=^D:

**Note** – The example shows connection to serial port B.

- 3. To use serial port A:

- a. Copy and paste the serial port B remote file.

- b. Modify the serial port B remote file as follows:

```

hardwire:\ dv=/dev/term/a:br#9600:el=^C^S^Q^U^D:ie=%$:oe=^D:

```

4. In a shell window on the Sun workstation, type tip hardwire.

```

hostname% tip hardwire connected

```

**Note** – The shell window is now a tip window directed to the serial port of the system unit being tested. When power is applied to the system unit being tested, POST messages will be displayed in this window.

- 5. When POST is completed, disconnect the tip window as follows:

- a. Open a shell window.

- **b.** Type ps -a to view the active tip line and process ID (PID) number.

- c. Type the following to kill the tip hardwire process.

% kill -9 PID#

### 3.2.2 Verifying the Baud Rate

To verify the baud rate between the system unit being tested and a terminal or another Sun workstation monitor:

- 1. Open a Shell window.

- 2. Type eeprom.

- 3. Verify the following serial port default settings as follows:

ttyb-mode = 9600,8,n,1

ttya-mode = 9600,8,n,1

**Note** – Ensure that the settings are consistent with TTY-type terminal or workstation monitor settings.

# 3.3 Initializing POST

POST is initilized in two ways:

- By setting the diag-switch? to true and the diag-level to max or min, followed by power cycling the system unit

- By simultaneously pressing the keyboard Stop and D keys while power is applied to the system unit

To set the diag-switch? to true and power cycle the system unit:

1. At the system prompt, type:

ok setenv diag-switch? true

2. At the keyboard, power cycle the system unit by simultaneously pressing the Shift key and the power-on key (FIGURE 3-2). After a few seconds, press the power-on key again.

FIGURE 3-2 Sun Type-5 Keyboard

#### 3. Verify the following:

- a. The display prompt is no longer displayed.

- b. The monitor power-on indicator flashes on and off.

- c. The keyboard Caps Lock key indicator flashes on and off.

#### 4. When the POST is complete, type the following at the system prompt:

ok setenv diag-switch? false

# 3.4 Maximum and Minimum Levels of POST

Two levels of POST are available: maximum (max) level and minimum (min) level. The system initiates the selected level of POST based upon the setting of diag-level, a NVRAM variable.

The default setting for diag-level is max. An example of a max level POST output on serial port A is provided in Section 3.4.1, "diag-level Variable Set to max" on page 3-7 An example of a min level POST output on serial port A is provided in Section 3.4.2, "diag-level Variable Set to min" on page 3-14.

To set the diag-level variable to min, type:

```

ok setenv diag-level min

```

To return to the default setting:

ok setenv diag-level max

### 3.4.1 diag-level Variable Set to max

When the diag-level variable is set to max, POST enables an extended set of diagnostic-level tests. This mode requires approximately 2 minutes and 15 seconds to complete (with 128 Mbytes of DIMM installed). CODE EXAMPLE 3-1 identifies a typical serial port A POST output with the diag-level variable set to max

CODE EXAMPLE 3-1 diag-level Variable Set to max

```

Executing Power On SelfTest

0>

0>@(#) Sun Ultra 60(UltraSPARC-II 2-way) UPA/PCI POST x.x.x

xx/xx/xxxx xx:xx PM

0>INFO: Processor 0 is master.

0>

0> <00> Init System BSS

0> <00> NVRAM Battery Detect Test

0> <00> NVRAM Scratch Addr Test

0> <00> DMMU TLB Tag Access Test

0> <00> DMMU TLB RAM Access Test

0> <00> IMMU TLB Tag Access Test

0> <00> IMMU TLB RAM Access Test

0> <00> Probe Ecache

0>INFO:CPU 296 MHz: 2048KB Ecache

0> <00> Ecache RAM Addr Test

0> <00> Ecache Tag Addr Test

0> <00> Ecache Tag Test

0> <00> Invalidate Ecache Tags

0>INFO: Processor 2 - UltraSPARC-II.

0> <00> Init SC Regs

0> <00> SC Address Reg Test

0> <00> SC Reg Index Test

0> <00> SC Regs Test

0> <00> SC Dtag RAM Addr Test

0> <00> SC Cache Size Init

0> <00> SC Dtag RAM Data Test

0> <00> SC Dtag Init

0> <00> Probe Memory

0>INFO:128MB Bank 0

0>INFO: 0MB Bank 1

0>INFO: 0MB Bank 2

0>INFO: 0MB Bank 3

0> <00> Malloc Post Memory

0> <00> Init Post Memory

0> <00> Post Memory Addr Test

0> <00> Map PROM/STACK/NVRAM in DMMU

0> <00>Memory Stack Test

```

2> <00> DMMU TLB Tag Access Test 2> <00> DMMU TLB RAM Access Test 2> <00> IMMU TLB Tag Access Test 2> <00> IMMU TLB RAM Access Test 2> <00> Probe Ecache 2>INFO:CPU 296 MHz: 2048KB Ecache 2> <00> Ecache RAM Addr Test 2> <00> Ecache Tag Addr Test 2> <00> Ecache Tag Test 2> <00> Invalidate Ecache Tags 2> <00> Map PROM/STACK/NVRAM in DMMU 2> <00> Update Slave Stack/Frame Ptrs 0> <00> DMMU Hit/Miss Test 0> <00> IMMU Hit/Miss Test 0> <00> DMMU Little Endian Test 0> <00> IU ASI Access Test 0> <00> FPU ASI Access Test 2> <00> DMMU Hit/Miss Test 2> <00> IMMU Hit/Miss Test 2> <00> DMMU Little Endian Test 2> <00> IU ASI Access Test 2> <00> FPU ASI Access Test 2> <00> Dcache RAM Test 2> <00> Dcache Tag Test 2> <00> Icache RAM Test 2> <00> Icache Tag Test 2> <00> Icache Next Test 2> <00> Icache Predecode Test 0> <1f> Init Psycho 0> <1f> PIO Read Error, Master Abort Test 0> <1f> PIO Read Error, Target Abort Test 0> <1f> PIO Write Error, Master Abort Test 0> <1f> PIO Write Error, Target Abort Test 0> <1f> Timer Increment Test 0> <1f> Consistent DMA UE ECC Rd Err Lpbk Test 0> <1f> Pass-Thru DMA UE ECC Rd Err Lpbk Test 0> <00> Copy Post to Memory 0> <00> Ecache Thrash Test 0> <00> Init Memory 0> <00> Memory Addr w/ Ecache Test 0>INFO:128MB Bank 0 0>INFO: 0MB Bank 1 0>INFO: 0MB Bank 2 0>INFO: 0MB Bank 3 0> <00> Block Memory Addr Test 0>INFO:128MB Bank 0 0>INFO: 0MB Bank 1

0>INFO: 0MB Bank 2 0>INFO: 0MB Bank 3 0> <00> ECC Memory Addr Test 0>INFO:128MB Bank 0 0>INFO: 0MB Bank 1 0>INFO: 0MB Bank 2 0>INFO: 0MB Bank 3 0> <00> Memory Status Test 0>INFO:128MB Bank 0 0>INFO: 0MB Bank 1 0>INFO: 0MB Bank 2 0>INFO: 0MB Bank 3 0> <00> V9 Instruction Test 0> <00> CPU Tick and Tick Compare Reg Test 0> <00> CPU Soft Trap Test 0> <00> CPU Softint Reg and Int Test 2> <00> V9 Instruction Test 2> <00> CPU Tick and Tick Compare Reg Test 0> <1f> Init Psycho 0> <1f> Psycho Cntl and UPA Reg Test 0> <1f> Psycho DMA Scoreboard Reg Test 0> <1f> Psycho Perf Cntl Reg Test 0> <1f> PIO Decoder and BCT Test 0> <1f> PCI Byte Enable Test 0> <1f> Counter/Timer Limit Regs Test 0> <1f> Timer Reload Test 0> <1f> Timer Periodic Test 0> <1f> Mondo Int Map (short) Reg Test 0> <1f> Mondo Int Set/Clr Reg Test 0> <1f> Psycho IOMMU Regs Test 0> <1f> Psycho IOMMU RAM Address Test 0> <1f> Psycho IOMMU CAM Address Test 0> <1f> IOMMU TLB Compare Test 0> <1f> IOMMU TLB Flush Test 0> <1f> Stream Buff A Control Reg Test 0> <1f> Psycho ScacheA Page Tag Addr Test 0> <1f> Psycho ScacheA Line Tag Addr Test 0> <1f> Psycho ScacheA RAM Addr Test 0> <1f> Psycho ScacheA Error Status NTA Test 0> <1f> Psycho ScacheB Page Tag Addr Test 0> <1f> Psycho ScacheB Line Tag Addr Test 0> <1f> Psycho ScacheB RAM Addr Test 0> <1f> Psycho ScacheB Error Status NTA Test 0> <1f> PBMA PCI Config Space Regs Test 0> <1f> PBMA Control/Status Reg Test 0> <1f> PBMA Diag Reg Test 0> <1f> PBMB PCI Config Space Regs Test

0> <1f> PBMB Control/Status Reg Test 0> <1f> PBMB Diag Reg Test 0> <00> FPU Regs Test 0> <00> FPU Move Regs Test 0> <00> FPU State Reg Test 0> <00> FPU Functional Test 0> <00> FPU Trap Test 0> <00> DMMU Primary Context Reg Test 0> <00> DMMU Secondary Context Reg Test 0> <00> DMMU TSB Reg Test 0> <00> DMMU Tag Access Reg Test 0> <00> DMMU VA Watchpoint Reg Test 0> <00> DMMU PA Watchpoint Reg Test 0> <00> IMMU TSB Reg Test 0> <00> IMMU Tag Access Reg Test 0> <00> DMMU TLB Tag Access Test 0> <00> DMMU TLB RAM Access Test 0> <00> Dcache RAM Test 0> <00> Dcache Tag Test 0> <00> Icache RAM Test 0> <00> Icache Tag Test 0> <00> Icache Next Test 0> <00> Icache Predecode Test 2> <00> FPU Regs Test 2> <00> FPU Move Regs Test 2> <00> FPU State Reg Test 2> <00> FPU Functional Test 2> <00> FPU Trap Test 2> <00> DMMU Primary Context Reg Test 2> <00> DMMU Secondary Context Reg Test 2> <00> DMMU TSB Reg Test 2> <00> DMMU Tag Access Reg Test 2> <00> DMMU VA Watchpoint Reg Test 2> <00> DMMU PA Watchpoint Reg Test 2> <00> IMMU TSB Reg Test 2> <00> IMMU Tag Access Reg Test 2> <00> DMMU TLB Tag Access Test 2> <00> DMMU TLB RAM Access Test 0> <00> CPU Addr Align Trap Test 0> <00> DMMU Access Priv Page Test 0> <00> DMMU Write Protected Page Test 0> <1f> Init Psycho 0> <1f> Pri CE ECC Error Test 0> <1f> Pri UE ECC Error Test 0> <1f> Pri 2 bit w/ bit hole UE ECC Err Test 0> <1f> Pri 3 bit UE ECC Err Test 0> <1f> Streaming DMA UE ECC Rd Err Ebus Test

| 0> <1f> Streaming DMA CE ECC Rd Err Ebus Test                     |

|-------------------------------------------------------------------|

| 0> <1f> Streaming DMA CE ECC Rd Err Lpbk Test                     |

| 0> <1f> Consistent DMA UE ECC Rd Error Ebus Test                  |

| 0> <1f> Consistent DMA UE ECC R/M/W Err Ebus Test                 |

|                                                                   |

| 0> <1f> Consistent DMA UE ECC R/M/W Err Lpbk Test                 |

| 0> <1f> Consistent DMA CE ECC Rd Err Ebus Test                    |

| 0> <1f> Consistent DMA CE ECC Rd Err Lpbk Test                    |

| 0> <1f> Consistent DMA CE ECC R/M/W Err Ebus Test                 |

| 0> <1f> Consistent DMA CE ECC R/M/W Err Lpbk Test                 |

| 0> <1f> Consistent DMA Wr Data Parity Err Lpbk Test               |

| 0> <1f> Pass-Thru DMA UE ECC Rd Err Ebus Test                     |

| 0> <1f> Pass-Thru DMA UE ECC R/M/W Err Ebus Test                  |

|                                                                   |

| 0> <1f> Pass-Thru DMA UE ECC R/M/W Err Lpbk Test                  |

| 0> <1f> Pass-Thru DMA CE ECC Rd Err Ebus Test                     |

| 0> <1f> Pass-Thru DMA CE ECC Rd Err Lpbk Test                     |

| 0> <1f> Pass-Thru DMA CE ECC R/M/W Err Ebus Test                  |

| 0> <1f> Pass-Thru DMA CE ECC R/M/W Err Lpbk Test                  |

| 0> <1f> Pass-Thru DMA Write Data Parity Err, Lpbk Test            |

| 0> <1f> Init Psycho                                               |

| -                                                                 |

| 0> <1f> Mondo Generate Interrupt Test                             |

| 0> <1f> Timer Interrupt Test                                      |

| 0> <1f> Timer Interrupt w/ periodic Test                          |

| 0> <1f> Psycho Stream Buff A Flush Sync Test                      |

| 0> <1f> Psycho Stream Buff B Flush Sync Test                      |

| 0> <1f> Psycho Stream Buff A Flush Invalidate Test                |

| 0> <1f> Psycho Stream Buff B Flush Invalidate Test                |

| 0> <1f> Psycho Merge Buffer w/ Scache A Test                      |

| 0> <1f> Psycho Merge Buffer w/ Scache B Test                      |

| 0> <1f> Consist DMA Rd, IOMMU miss Ebus Test                      |

| 0> <1f> Consist DMA Rd, IOMMU miss Lpbk Test                      |

|                                                                   |

| 0> <1f> Consist DMA Rd, IOMMU hit Ebus Test                       |

| 0> <1f> Consist DMA Rd, IOMMU hit Lpbk Test                       |

| 0> <1f> Consist DMA Wr, IOMMU miss Ebus Test                      |

| 0> <1f> Consist DMA Wr, IOMMU miss Lpbk Test                      |

| 0> <1f> Consist DMA Wr, IOMMU hit Ebus Test                       |

| 0> <1f> Consist DMA Wr, IOMMU hit Lpbk Test                       |

| 0> <1f> Stream DMA Rd, IOMMU miss, Scache Miss Ebus Test          |

| 0> <1f> Stream DMA Rd, IOMMU miss, Scache Miss Lpbk Test          |

| 0> <1f> Stream DMA Rd, IOMMU hit, Scache Miss Ebus Test           |

| 0> <1f> Stream DMA Rd, IOMMU hit, Scache Miss Lpbk Test           |

|                                                                   |

| 0> <1f> Stream DMA Rd, IOMMU Miss, Scache(prev rd) Hit Ebus Test  |

| 0> <1f> Stream DMA Rd, IOMMU Miss, Scache Hit (prev rd) Lpbk Test |

| 0> <1f> Stream DMA Rd, IOMMU Hit, Scache Hit Ebus Test            |

| 0> <1f> Stream DMA Rd, IOMMU Hit, Scache Hit (prev rd) Lpbk Test  |

| 0> <1f> Stream DMA Rd, IOMMU Miss, Scache Hit(prev wr) Ebus Test  |

| 0> <1f> Stream DMA Rd, IOMMU Miss, Scache Hit (prev wr) Lpbk Test |

| 0> <1f> Stream DMA Rd, IOMMU Hit, Scache Hit(prev wr) Ebus Test   |

|                                                                   |

0> <1f> Stream DMA Rd, IOMMU Hit, Scache Hit (prev wr) Lpbk Test 0> <1f> Stream DMA Wr, IOMMU miss, Scache Miss Ebus Test 0> <1f> Stream DMA Wr, IOMMU miss, Scache Miss Lpbk Test 0> <1f> Stream DMA Wr, IOMMU hit, Scache Miss Ebus Test 0> <1f> Stream DMA Wr, IOMMU hit, Scache Miss Lpbk Test 0> <1f> Stream DMA Wr, IOMMU Miss, Scache(prev rd) Hit Ebus Test 0> <1f> Stream DMA Wr, IOMMU Miss, Scache(prev rd) Hit Lpbk Test 0> <1f> Stream DMA Wr, IOMMU Hit, Scache(prev rd) Hit Ebus Test 0> <1f> Stream DMA Wr, IOMMU Hit, Scache(prev rd) Hit Lpbk Test 0> <1f> Stream DMA Wr, IOMMU Miss, Scache(prev wr) Hit Ebus Test 0> <1f> Stream DMA Wr, IOMMU Miss, Scache(prev wr) Hit Lpbk Test 0> <1f> Stream DMA Wr, IOMMU Hit, Scache(prev wr) Hit Ebus Test 0> <1f> Stream DMA Wr, IOMMU Hit, Scache(prev wr) Hit Lpbk Test 0> <1f> Pass-Thru DMA Rd, Ebus device Test 0> <1f> Pass-Thru DMA Rd, Loopback Mode Test 0> <1f> Pass-Thru DMA Wr, Ebus device Test 0> <1f> Pass-Thru DMA Wr, Loopback Mode Test 0> <1f> Consist DMA Rd, IOMMU LRU Lock Ebus Test 0> <1f> Consist DMA Rd, IOMMU LRU Lock Lpbk Test 0> <1f> Stream DMA Rd, IOMMU LRU Lock, Scache LRU Lock Ebus Test 0> <1f> Stream DMA Rd, IOMMU LRU Lock, Scache LRU Lock Lpbk Test 0> <1f> Stream DMA Rd, IOMMU miss, Scache LRU Lock Ebus Test 0> <1f> Stream DMA Rd, IOMMU Miss, Scache LRU Lock Lpbk Test 0> <1f> Stream DMA Rd, IOMMU Hit, Scache LRU Lock Ebus Test 0> <1f> Stream DMA Rd, IOMMU Hit, Scache LRU Lock Lpbk Test 0> <1f> Stream DMA Rd, IOMMU LRU Lock, Scache Miss Ebus Test 0> <1f> Stream DMA Rd, IOMMU LRU Lock, Scache Miss Lpbk Test 0> <1f> Consist DMA Wr, IOMMU LRU Locked Ebus Test 0> <1f> Consist DMA Wr, IOMMU LRU Lock Lpbk Test 0> <1f> Stream DMA Wr, IOMMU LRU Lock, Scache LRU Lock Ebus Test 0> <1f> Stream DMA Wr, IOMMU LRU Lock, Scache LRU Lock Lpbk Test 0> <1f> Stream DMA Wr, IOMMU Miss, Scache LRU Lock Ebus Test 0> <1f> Stream DMA Wr, IOMMU Miss, Scache LRU Lock Lpbk Test 0> <1f> Stream DMA Wr, IOMMU Hit, Scache LRU Lock Ebus Test 0> <1f> Stream DMA Wr, IOMMU Hit, Scache LRU Lock Lpbk Test 0> <1f> Stream DMA Wr, IOMMU LRU Lock, Scache Miss Ebus Test 0> <1f> Stream DMA Wr, IOMMU LRU Lock, Scache Miss Lpbk Test 0> <1f> Stream DMA Wr, IOMMU LRU Lock, Scache(prev rd) Hit Ebus Test 0> <1f> Stream DMA Wr, IOMMU LRU Lock, Scache(prev rd) Hit Lpbk Test 0> <00> Init Memory 0>INFO:128MB Bank 0 0>INFO: 0MB Bank 1 0>INFO: 0MB Bank 2 0>INFO: 0MB Bank 3 0> <00> Memory w/ Ecache Test

```

0>INFO:128MB Bank 0

0>INFO: 0MB Bank 1

0>INFO: 0MB Bank 2

0>INFO: 0MB Bank 3

0> <00> Block Memory Test

0>INFO:128MB Bank 0

0>INFO: OMB Bank 1

0>INFO: 0MB Bank 2

0>INFO: 0MB Bank 3

0> <00> ECC Blk Memory Test

0>INFO:128MB Bank 0

0>INFO: 0MB Bank 1

0>INFO: 0MB Bank 2

0>INFO: 0MB Bank 3

0> <00> UltraSPARC-2 Prefetch Instructions Test

0> <00>Test 0: prefetch_mr

0> <00>Test 1: prefetch to non-cacheable page

0> <00>Test 2: prefetch to page with dmmu misss

0> <00>Test 3: prefetch miss does not check alignment

0> <00>Test 4: prefetcha with asi 0x4c is noped

0> <00>Test 5: prefetcha with asi 0x54 is noped

0> <00>Test 6: prefetcha with asi 0x6e is noped

0 > < 00 > Test 7: prefetcha with asi 0x76 is noped

0> <00>Test 8: prefetch with fcn 5

0> <00>Test 9: prefetch with fcn 2

0> <00>Test 10: prefetch with fcn 12

0> <00>Test 11: prefetch with fcn 16 is noped

0> <00>Test 12: prefetch with fcn 29 is noped

0> <00>Test 13: prefetcha with asi 0x15 is noped

0> <00>Test 14: prefetch with fcn 3

0> <00>Test 15: prefetchal4 with fcn 2

0> <00>Test 16: prefetcha80_mr

0> <00>Test 17: prefetcha81 1r

0> <00>Test 18: prefetchal0 mw

0> <00>Test 19: prefetcha80_17 is noped

0> <00>Test 20: prefetcha10_6: illegal instruction trap

0> <00>Test 21: prefetchall 1w

0> <00>Test 22: prefetcha81_31

0> <00>Test 23: prefetchal1_15: illegal instruction trap

2> <00> UltraSPARC-2 Prefetch Instructions Test

2> <00>Test 0: prefetch_mr

2> <00>Test 1: prefetch to non-cacheable page

2> <00>Test 2: prefetch to page with dmmu misss

2> <00>Test 3: prefetch miss does not check alignment

2> <00>Test 4: prefetcha with asi 0x4c is noped

2> <00>Test 5: prefetcha with asi 0x54 is noped

2> <00>Test 6: prefetcha with asi 0x6e is noped

```

```

2> <00>Test 7: prefetcha with asi 0x76 is noped

2> <00>Test 8: prefetch with fcn 5

2> <00>Test 9: prefetch with fcn 2

2> <00>Test 10: prefetch with fcn 12

2> <00>Test 11: prefetch with fcn 16 is noped

2> <00>Test 12: prefetch with fcn 29 is noped

2> <00>Test 13: prefetcha with asi 0x15 is noped

2> <00>Test 14: prefetch with fcn 3

2> <00>Test 15: prefetchal4 with fcn 2

2> <00>Test 16: prefetcha80 mr

2> <00>Test 17: prefetcha81_1r

2> <00>Test 18: prefetchal0_mw

2> <00>Test 19: prefetcha80 17 is noped

2> <00>Test 20: prefetcha10_6: illegal instruction trap

2> <00>Test 21: prefetchal1_1w

2> <00>Test 22: prefetcha81_31

2> <00>Test 23: prefetchal1_15: illegal instruction trap

0>STATUS =PASSED

Power On Selftest Completed

```

### 3.4.2 diag-level Variable Set to min

When the diag-level variable is set to min, POST enables an abbreviated set of diagnostic-level tests. This mode requires approximately 1 minute and 30 seconds to complete (with 128 Mbytes of DIMM installed). CODE EXAMPLE 3-2 identifies a serial port A POST output with the diag-level NVRAM variable set to min.

```

CODE EXAMPLE 3-2 diag-level Variable Set to min

```

```

Executing Power On SelfTest

0>

0>@(#) Sun Ultra 60(UltraSPARC-II 2-way) UPA/PCI POST x.x.x

xx/xx/xxxx xx:xx PM

0>INFO: Processor 0 is master.

0>

0> <00> Init System BSS

0> <00> Init System BSS

0> <00> NVRAM Battery Detect Test

0> <00> NVRAM Scratch Addr Test

0> <00> NVRAM Scratch Addr Test

0> <00> DMMU TLB Tag Access Test

0> <00> DMMU TLB RAM Access Test

0> <00> IMMU TLB Tag Access Test

0> <00> IMMU TLB Tag Access Test

```

0> <00> IMMU TLB RAM Access Test 0> <00> Probe Ecache 0>INFO:CPU 296 MHz: 2048KB Ecache 0> <00> Ecache RAM Addr Test 0> <00> Ecache Tag Addr Test 0> <00> Ecache Tag Test 0> <00> Invalidate Ecache Tags 0>INFO: Processor 2 - UltraSPARC-II. 0> <00> Init SC Regs 0> <00> SC Address Reg Test 0> <00> SC Reg Index Test 0> <00> SC Regs Test 0> <00> SC Dtag RAM Addr Test 0> <00> SC Cache Size Init 0> <00> SC Dtag RAM Data Test 0> <00> SC Dtag Init 0> <00> Probe Memory 0>INFO:128MB Bank 0 0>INFO: 0MB Bank 1 0>INFO: 0MB Bank 2 0>INFO: OMB Bank 3 0> <00> Malloc Post Memory 0> <00> Init Post Memory 0> <00> Post Memory Addr Test 0> <00> Map PROM/STACK/NVRAM in DMMU 0> <00>Memory Stack Test 2> <00> DMMU TLB Tag Access Test 2> <00> DMMU TLB RAM Access Test 2> <00> IMMU TLB Tag Access Test 2> <00> IMMU TLB RAM Access Test 2> <00> Probe Ecache 2>INFO:CPU 296 MHz: 2048KB Ecache 2> <00> Ecache RAM Addr Test 2> <00> Ecache Tag Addr Test 2> <00> Ecache Tag Test 2> <00> Invalidate Ecache Tags 2> <00> Map PROM/STACK/NVRAM in DMMU 2> <00> Update Slave Stack/Frame Ptrs 0> <00> DMMU Hit/Miss Test 0> <00> IMMU Hit/Miss Test 0> <00> DMMU Little Endian Test 0> <00> IU ASI Access Test 0> <00> FPU ASI Access Test 2> <00> DMMU Hit/Miss Test 2> <00> IMMU Hit/Miss Test 2> <00> DMMU Little Endian Test 2> <00> IU ASI Access Test

2> <00> FPU ASI Access Test 2> <00> Dcache RAM Test 2> <00> Dcache Tag Test 2> <00> Icache RAM Test 2> <00> Icache Tag Test 2> <00> Icache Next Test 2> <00> Icache Predecode Test 0> <1f> Init Psycho 0> <1f> PIO Read Error, Master Abort Test 0> <1f> PIO Read Error, Target Abort Test 0> <1f> PIO Write Error, Master Abort Test 0> <1f> PIO Write Error, Target Abort Test 0> <1f> Timer Increment Test 0> <1f> Consistent DMA UE ECC Rd Err Lpbk Test 0> <1f> Pass-Thru DMA UE ECC Rd Err Lpbk Test 0> <00> Copy Post to Memory 0> <00> Ecache Thrash Test 0> <00> Init Memory 0> <00> Memory Addr w/ Ecache Test 0>INFO:128MB Bank 0 0>INFO: OMB Bank 1 0>INFO: 0MB Bank 2 0>INFO: 0MB Bank 3 0> <00> Block Memory Addr Test 0>INFO:128MB Bank 0 0>INFO: 0MB Bank 1 0>INFO: 0MB Bank 2 0>INFO: OMB Bank 3 0> <00> ECC Memory Addr Test 0>INFO:128MB Bank 0 0>INFO: OMB Bank 1 0>INFO: 0MB Bank 2 0>INFO: 0MB Bank 3 0> <00> Memory Status Test 0>INFO:128MB Bank 0 0>INFO: 0MB Bank 1 0>INFO: 0MB Bank 2 0>INFO: 0MB Bank 3 0> <00> V9 Instruction Test 0> <00> CPU Tick and Tick Compare Reg Test 0> <00> CPU Soft Trap Test 0> <00> CPU Softint Reg and Int Test 2> <00> V9 Instruction Test 2> <00> CPU Tick and Tick Compare Reg Test 0> <1f> Init Psycho 0> <1f> Psycho Cntl and UPA Reg Test 0> <1f> Psycho DMA Scoreboard Reg Test

0> <1f> Psycho Perf Cntl Reg Test 0> <1f> PIO Decoder and BCT Test 0> <1f> PCI Byte Enable Test 0> <1f> Counter/Timer Limit Regs Test 0> <1f> Timer Reload Test 0> <1f> Timer Periodic Test 0> <1f> Mondo Int Map (short) Reg Test 0> <1f> Mondo Int Set/Clr Reg Test 0> <1f> Psycho IOMMU Regs Test 0> <1f> Psycho IOMMU RAM Address Test 0> <1f> Psycho IOMMU CAM Address Test 0> <1f> IOMMU TLB Compare Test 0> <1f> IOMMU TLB Flush Test 0> <1f> Stream Buff A Control Reg Test 0> <1f> Psycho ScacheA Page Tag Addr Test 0> <1f> Psycho ScacheA Line Tag Addr Test 0> <1f> Psycho ScacheA RAM Addr Test 0> <1f> Psycho ScacheA Error Status NTA Test 0> <1f> Psycho ScacheB Page Tag Addr Test 0> <1f> Psycho ScacheB Line Tag Addr Test 0> <1f> Psycho ScacheB RAM Addr Test 0> <1f> Psycho ScacheB Error Status NTA Test 0> <1f> PBMA PCI Config Space Regs Test 0> <1f> PBMA Control/Status Reg Test 0> <1f> PBMA Diag Reg Test 0> <1f> PBMB PCI Config Space Regs Test 0> <1f> PBMB Control/Status Reg Test 0> <1f> PBMB Diag Reg Test 0> <00> UltraSPARC-2 Prefetch Instructions Test 0> <00>Test 0: prefetch mr 0> <00>Test 1: prefetch to non-cacheable page 0> <00>Test 2: prefetch to page with dmmu misss 0> <00>Test 3: prefetch miss does not check alignment 0> <00>Test 4: prefetcha with asi 0x4c is noped 0> <00>Test 5: prefetcha with asi 0x54 is noped 0> <00>Test 6: prefetcha with asi 0x6e is noped 0> <00>Test 7: prefetcha with asi 0x76 is noped 0> <00>Test 8: prefetch with fcn 5 0> <00>Test 9: prefetch with fcn 2 0> <00>Test 10: prefetch with fcn 12 0> <00>Test 11: prefetch with fcn 16 is noped 0> <00>Test 12: prefetch with fcn 29 is noped 0> <00>Test 13: prefetcha with asi 0x15 is noped 0> <00>Test 14: prefetch with fcn 3 0> <00>Test 15: prefetchal4 with fcn 2 0> <00>Test 16: prefetcha80\_mr 0> <00>Test 17: prefetcha81\_1r

```

0> <00>Test 18: prefetchal0 mw

0> <00>Test 19: prefetcha80_17 is noped

0> <00>Test 20: prefetcha10_6: illegal instruction trap

0> <00>Test 21: prefetchall 1w

0> <00>Test 22: prefetcha81_31

0> <00>Test 23: prefetchal1_15: illegal instruction trap

2> <00> UltraSPARC-2 Prefetch Instructions Test

2> <00>Test 0: prefetch_mr

2> <00>Test 1: prefetch to non-cacheable page

2> <00>Test 2: prefetch to page with dmmu misss

2> <00>Test 3: prefetch miss does not check alignment

2> <00>Test 4: prefetcha with asi 0x4c is noped

2> <00>Test 5: prefetcha with asi 0x54 is noped

2> <00>Test 6: prefetcha with asi 0x6e is noped

2> <00>Test 7: prefetcha with asi 0x76 is noped

2> <00>Test 8: prefetch with fcn 5

2> <00>Test 9: prefetch with fcn 2

2> <00>Test 10: prefetch with fcn 12

2> <00>Test 11: prefetch with fcn 16 is noped

2> <00>Test 12: prefetch with fcn 29 is noped

2> <00>Test 13: prefetcha with asi 0x15 is noped

2> <00>Test 14: prefetch with fcn 3

2> <00>Test 15: prefetchal4 with fcn 2

2> <00>Test 16: prefetcha80 mr

2> <00>Test 17: prefetcha81_1r

2> <00>Test 18: prefetchal0_mw

2> <00>Test 19: prefetcha80_17 is noped

2> <00>Test 20: prefetcha10 6: illegal instruction trap

2> <00>Test 21: prefetchal1_1w

2> <00>Test 22: prefetcha81 31

2> <00>Test 23: prefetchall 15: illegal instruction trap

0>STATUS = PASSED

Power On Selftest Completed

```

### 3.4.3 POST Progress and Error Reporting

While POST is initialized, the Caps Lock key on the Sun Type-5 keyboard flashes on and off to indicate that POST tests are being executed. Additional POST progress indications are also visible when a TTY-type terminal or a tip line is connected between serial port A (default port) of the system being tested and a POST monitoring system. If an error occurs during the POST execution, the keyboard Caps Lock key indicator stops flashing and an error code is displayed using the Caps Lock, Compose, Scroll Lock, and Num Lock key indicators. The error code indicates a particular system hardware failure.

**Note** – An error code may only be visible for a few seconds. Observe the Caps Lock, Compose, Scroll Lock, and Num Lock key indicators closely while POST is active.

In most cases, POST also attempts to send a failure message to the POST monitoring system. CODE EXAMPLE 3-3 identifies the typical appearance of a failure message. If a keyboard error code is displayed, determine the meaning of the error code by comparing the keyboard error code pattern to the corresponding error code meaning listed in TABLE 3-2.

**Note** – The system unit does not automatically boot if a POST error occurs; it halts at the ok prompt to alert the user of a failure.

CODE EXAMPLE 3-3 Typical Error Code Failure Message

```

Executing Power On SelfTest

0>

0>@(#) Sun UltraSPARC-II 2-way(Deuterium) UPA/PCI POST 1.0.3

08/15/97: 11:36

0>INFO: Processor 0 is master.

0>

0> <00> Init System BSS

0> <00> NVRAM Battery Detect Test

0> <00> NVRAM Scratch Addr Test

0> <00> DMMU TLB Tag Access Test

0> <00> DMMU TLB RAM Access Test

0> <00> Probe Ecache

0>INFO:CPU 296 MHz: 2048KB Ecache

0> <00> Ecache RAM Addr Test

0> <00> Ecache Tag Addr Test

0> <00> Invalidate Ecache Tags

0>INFO: Min Psycho configuration.

0>INFO: Processor 2 - UltraSPARC-II.

0> <00> Init SC Regs

0> <00> SC Address Reg Test

0> <00> SC Reg Index Test

0> <00> SC Regs Test

0> <00> SC Dtag RAM Addr Test

0> <00> SC Cache Size Init

```

```

CODE EXAMPLE 3-3 Typical Error Code Failure Message (Continued)

```

```

0> <00> SC Dtag Init

0> <00> Probe Memory

0>INFO:128MB Bank 0

0>INFO:No memory detected in Bank 1

0>INFO:No memory detected in Bank 2

0>INFO:No memory detected in Bank 3

0> <00> Malloc Post Memory

0> <00> Init Post Memory

0> <00> Post Memory Addr Test

0>mem utils.c mem err bd desc = 00000000.00000000, xor =

80808000.80808080

0>STATUS =FAILED

0>TEST =Post Memory Addr

TTF = 0

PASSES =1

ERRORS =1

SUSPECT=SIMM U0801

0>MESSAGE=Mem Addr line compare error

addr 0000000.0000000

exp 0000000.0000000

obs 80808000.80808080

0> xor 80808000.80808080

0> Verbose Data Path Information:

0 > Addr = 0000000.0000000

0> PATH SUSPECT= SDB U0301

0> PATH SUSPECT= XBAR U301

0> <00>Memory Stack Test

0>STATUS =FAILED

0>TEST =Post Memory Addr

TTF

=0

PASSES =1

ERRORS =1

SUSPECT=SIMM U0801

0>MESSAGE=Memory compare error

addr 0000000.007f8080

exp 55555555.557fd5d5

obs 15151515.15151505

```

| Caps Lock | Compose | Scroll Lock | Num Lock | Meaning of Pattern |

|-----------|---------|-------------|----------|--------------------|

| On        | Off     | Off         | Off      | System motherboard |

| Off       | On      | Off         | Off      | CPU module 0       |

| Off       | On      | On          | Off      | CPU module 1       |

| On        | Off     | Off         | On       | No memory detected |

| On        | On      | Off         | Off      | Memory bank 0      |

| On        | On      | Off         | On       | Memory bank 1      |

| On        | On      | On          | Off      | Memory bank 2      |

| On        | On      | On          | On       | Memory bank 3      |

| Off       | Off     | Off         | On       | NVRAM              |

#### TABLE 3-2 Keyboard LED Patterns

# 3.5 Bypassing POST

POST can be disabled and thereby bypassed. To bypass POST:

- **1.** Prior to powering on the system, press and hold the Stop key on the keyboard (FIGURE 3-2).

- 2. With the Stop key pressed, turn on the system by pressing the power-on key.

# 3.6 Additional Keyboard Control Commands

Stop Key

If the diag-level is set to either max or min and the diag-level switch? variable is set to true and POST is not to be executed when the system is powered on, press and hold the keyboard Stop key and press the keyboard power-on key.

**Note** – Press and hold the Stop key for approximately 5 seconds.

Stop and N Keys

To set the system NVRAM parameters to the original default settings, press and hold the Stop and N keys before powering on the system. Continue to hold the Stop and N keys until the system banner displays on the monitor.

# 3.7 System and Keyboard LEDs

The power light-emitting diode (LED), located at the chassis front, remains lighted when the system is operating normally. FIGURE 1-2 shows the location of the power LED.

While POST is executing and making progress, the Caps Lock key LED blinks while the rest of the LEDs are off. If POST finds an error, a pattern is encoded in the LEDs to indicate the defective part. If POST completes with no errors, all LEDs will be off and the system will return to the OpenBoot PROM (OBP). TABLE 3-2 defines the keyboard LED patterns. FIGURE 3-2 shows the location of the LED keys on the keyboard.

# 3.8 Initializing Motherboard POST

To initialize the motherboard POST:

- 1. Power off the system unit.